Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 1: Introduction<br />

Configurable receive address filter for unicast, general, and broadcast addresses<br />

Media Independent Interface (MII), Gigabit Media Independent Interface (GMII), and<br />

Reduced Gigabit Media Independent Interface (RGMII)<br />

1000BASE-X Physical Coding Sublayer (PCS) and a Physical Medium Attachment<br />

(PMA) sublayer included for use with the <strong>Virtex</strong>-5 RocketIO serial transceivers to<br />

provide a complete on-chip 1000BASE-X implementation<br />

Serial Gigabit Media Independent Interface (SGMII) supported through the RocketIO<br />

serial transceivers’ interfaces to external copper PHY layer for full-duplex operation<br />

Typical <strong>Ethernet</strong> Application Overview<br />

Typical applications for the <strong>Ethernet</strong> <strong>MAC</strong> include:<br />

“<strong>Ethernet</strong> Switch or Router”<br />

“<strong>Ethernet</strong> Communications Port for an <strong>Embedded</strong> Processor”<br />

<strong>Ethernet</strong> Switch or Router<br />

<strong>Virtex</strong>-5 Device<br />

Switch or<br />

Router<br />

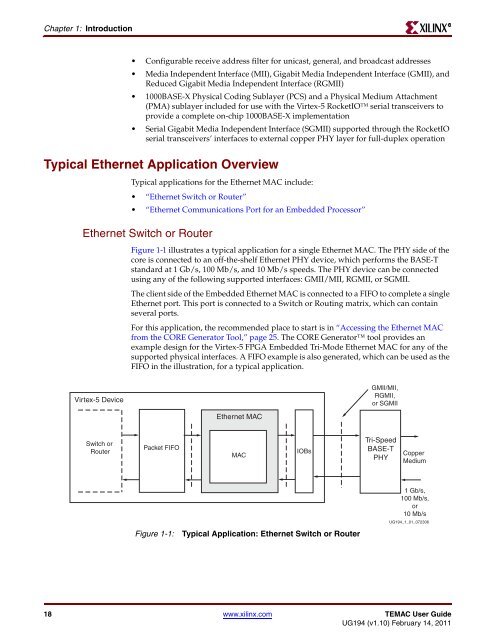

Figure 1-1 illustrates a typical application for a single <strong>Ethernet</strong> <strong>MAC</strong>. The PHY side of the<br />

core is connected to an off-the-shelf <strong>Ethernet</strong> PHY device, which performs the BASE-T<br />

standard at 1 Gb/s, 100 Mb/s, and 10 Mb/s speeds. The PHY device can be connected<br />

using any of the following supported interfaces: GMII/MII, RGMII, or SGMII.<br />

The client side of the <strong>Embedded</strong> <strong>Ethernet</strong> <strong>MAC</strong> is connected to a FIFO to complete a single<br />

<strong>Ethernet</strong> port. This port is connected to a Switch or Routing matrix, which can contain<br />

several ports.<br />

For this application, the recommended place to start is in “Accessing the <strong>Ethernet</strong> <strong>MAC</strong><br />

from the CORE Generator Tool,” page 25. The CORE Generator tool provides an<br />

example design for the <strong>Virtex</strong>-5 <strong>FPGA</strong> <strong>Embedded</strong> <strong>Tri</strong>-<strong>Mode</strong> <strong>Ethernet</strong> <strong>MAC</strong> for any of the<br />

supported physical interfaces. A FIFO example is also generated, which can be used as the<br />

FIFO in the illustration, for a typical application.<br />

Packet FIFO<br />

<strong>Ethernet</strong> <strong>MAC</strong><br />

<strong>MAC</strong><br />

Figure 1-1: Typical Application: <strong>Ethernet</strong> Switch or Router<br />

GMII/MII,<br />

RGMII,<br />

or SGMII<br />

Copper<br />

Medium<br />

18 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

IOBs<br />

<strong>Tri</strong>-Speed<br />

BASE-T<br />

PHY<br />

1 Gb/s,<br />

100 Mb/s,<br />

or<br />

10 Mb/s<br />

<strong>UG194</strong>_1_01_072306<br />

R