Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

R<br />

Transmitting a PAUSE Control Frame<br />

Flow Control Block<br />

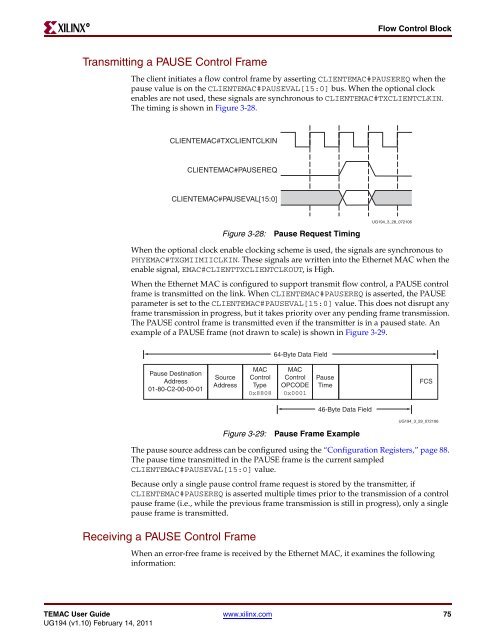

The client initiates a flow control frame by asserting CLIENTE<strong>MAC</strong>#PAUSEREQ when the<br />

pause value is on the CLIENTE<strong>MAC</strong>#PAUSEVAL[15:0] bus. When the optional clock<br />

enables are not used, these signals are synchronous to CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN.<br />

The timing is shown in Figure 3-28.<br />

CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN<br />

CLIENTE<strong>MAC</strong>#PAUSEVAL[15:0]<br />

When the optional clock enable clocking scheme is used, the signals are synchronous to<br />

PHYE<strong>MAC</strong>#TXGMIIMIICLKIN. These signals are written into the <strong>Ethernet</strong> <strong>MAC</strong> when the<br />

enable signal, E<strong>MAC</strong>#CLIENTTXCLIENTCLKOUT, is High.<br />

When the <strong>Ethernet</strong> <strong>MAC</strong> is configured to support transmit flow control, a PAUSE control<br />

frame is transmitted on the link. When CLIENTE<strong>MAC</strong>#PAUSEREQ is asserted, the PAUSE<br />

parameter is set to the CLIENTE<strong>MAC</strong>#PAUSEVAL[15:0] value. This does not disrupt any<br />

frame transmission in progress, but it takes priority over any pending frame transmission.<br />

The PAUSE control frame is transmitted even if the transmitter is in a paused state. An<br />

example of a PAUSE frame (not drawn to scale) is shown in Figure 3-29.<br />

Pause Destination<br />

Address<br />

01-80-C2-00-00-01<br />

CLIENTE<strong>MAC</strong>#PAUSEREQ<br />

The pause source address can be configured using the “Configuration Registers,” page 88.<br />

The pause time transmitted in the PAUSE frame is the current sampled<br />

CLIENTE<strong>MAC</strong>#PAUSEVAL[15:0] value.<br />

Because only a single pause control frame request is stored by the transmitter, if<br />

CLIENTE<strong>MAC</strong>#PAUSEREQ is asserted multiple times prior to the transmission of a control<br />

pause frame (i.e., while the previous frame transmission is still in progress), only a single<br />

pause frame is transmitted.<br />

Receiving a PAUSE Control Frame<br />

Figure 3-28: Pause Request Timing<br />

Source<br />

Address<br />

<strong>MAC</strong><br />

Control<br />

Type<br />

0x8808<br />

64-Byte Data Field<br />

<strong>MAC</strong><br />

Control<br />

OPCODE<br />

0x0001<br />

Figure 3-29: Pause Frame Example<br />

<strong>UG194</strong>_3_28_072106<br />

When an error-free frame is received by the <strong>Ethernet</strong> <strong>MAC</strong>, it examines the following<br />

information:<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 75<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

Pause<br />

Time<br />

46-Byte Data Field<br />

FCS<br />

<strong>UG194</strong>_3_29_072106