Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

R<br />

<strong>Ethernet</strong> <strong>MAC</strong> Signal Descriptions<br />

<strong>Ethernet</strong> <strong>MAC</strong> Signal Descriptions<br />

This section defines all of the <strong>Ethernet</strong> <strong>MAC</strong> primitive signals. The signals are divided into<br />

the following categories:<br />

“Client-Side Signals”<br />

“Host Interface Signals”<br />

“Management Data Input/Output (MDIO) Signals”<br />

“MII/GMII/RGMII Physical Interface Signals”<br />

“RocketIO Serial Transceiver Signals”<br />

“Global Clock and Reset Signals”<br />

All the signals available in the <strong>Ethernet</strong> <strong>MAC</strong> primitive are described in this section. The #<br />

symbol denotes the E<strong>MAC</strong>0 or E<strong>MAC</strong>1 signals.<br />

Client-Side Signals<br />

TX Client Signals<br />

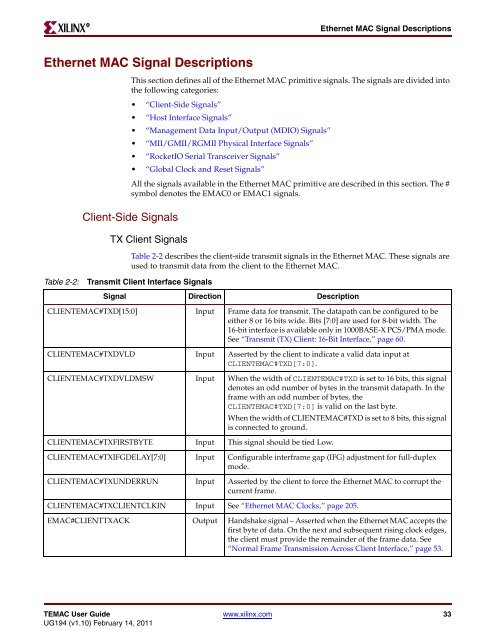

Table 2-2: Transmit Client Interface Signals<br />

Table 2-2 describes the client-side transmit signals in the <strong>Ethernet</strong> <strong>MAC</strong>. These signals are<br />

used to transmit data from the client to the <strong>Ethernet</strong> <strong>MAC</strong>.<br />

Signal Direction Description<br />

CLIENTE<strong>MAC</strong>#TXD[15:0] Input Frame data for transmit. The datapath can be configured to be<br />

either 8 or 16 bits wide. Bits [7:0] are used for 8-bit width. The<br />

16-bit interface is available only in 1000BASE-X PCS/PMA mode.<br />

See “Transmit (TX) Client: 16-Bit Interface,” page 60.<br />

CLIENTE<strong>MAC</strong>#TXDVLD Input Asserted by the client to indicate a valid data input at<br />

CLIENTE<strong>MAC</strong>#TXD[7:0].<br />

CLIENTE<strong>MAC</strong>#TXDVLDMSW Input When the width of CLIENTE<strong>MAC</strong>#TXD is set to 16 bits, this signal<br />

denotes an odd number of bytes in the transmit datapath. In the<br />

frame with an odd number of bytes, the<br />

CLIENTE<strong>MAC</strong>#TXD[7:0] is valid on the last byte.<br />

When the width of CLIENTE<strong>MAC</strong>#TXD is set to 8 bits, this signal<br />

is connected to ground.<br />

CLIENTE<strong>MAC</strong>#TXFIRSTBYTE Input This signal should be tied Low.<br />

CLIENTE<strong>MAC</strong>#TXIFGDELAY[7:0] Input Configurable interframe gap (IFG) adjustment for full-duplex<br />

mode.<br />

CLIENTE<strong>MAC</strong>#TXUNDERRUN Input Asserted by the client to force the <strong>Ethernet</strong> <strong>MAC</strong> to corrupt the<br />

current frame.<br />

CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN Input See “<strong>Ethernet</strong> <strong>MAC</strong> Clocks,” page 205.<br />

E<strong>MAC</strong>#CLIENTTXACK Output Handshake signal – Asserted when the <strong>Ethernet</strong> <strong>MAC</strong> accepts the<br />

first byte of data. On the next and subsequent rising clock edges,<br />

the client must provide the remainder of the frame data. See<br />

“Normal Frame Transmission Across Client Interface,” page 53.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 33<br />

<strong>UG194</strong> (v1.10) February 14, 2011