Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

MDC<br />

MDIO<br />

R<br />

MDIO Transactions<br />

Introduction to MDIO<br />

All transactions, read or write, are initiated by the MDIO master. All MDIO slave devices,<br />

when addressed, must respond. MDIO transactions take the form of an MDIO frame,<br />

containing fields for transaction type, address and data. This MDIO frame is transferred<br />

across the MDIO wire synchronously to MDC. The following abbreviations are used in this<br />

chapter:<br />

Table 5-1: Abbreviations Used in this Chapter<br />

Abbreviation Definition<br />

Write Transaction<br />

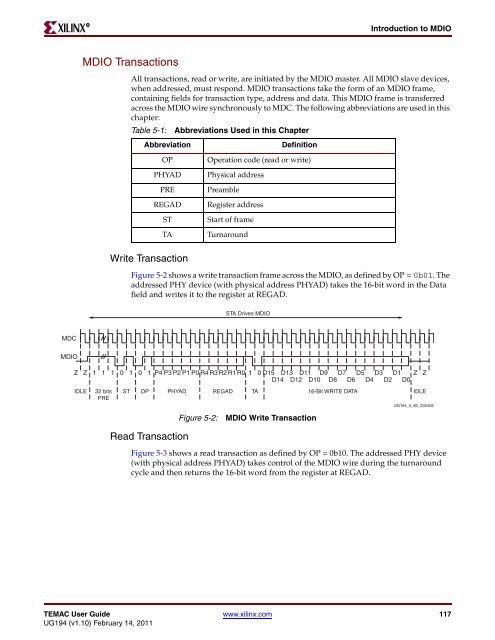

Figure 5-2 shows a write transaction frame across the MDIO, as defined by OP = 0b01. The<br />

addressed PHY device (with physical address PHYAD) takes the 16-bit word in the Data<br />

field and writes it to the register at REGAD.<br />

Read Transaction<br />

OP Operation code (read or write)<br />

PHYAD Physical address<br />

PRE Preamble<br />

REGAD Register address<br />

ST Start of frame<br />

TA Turnaround<br />

STA Drives MDIO<br />

Z Z 1 1 1 0 1 0 1 P4 P3 P2 P1 P0 R4 R3 R2 R1 R0 1 0 D15 D13 D11 D9 D7 D5 D3 D1 Z Z<br />

D14 D12 D10 D8 D6 D4 D2 D0<br />

IDLE 32 bits<br />

PRE<br />

ST OP PHYAD REGAD TA 16-Bit WRITE DATA<br />

IDLE<br />

Figure 5-2: MDIO Write Transaction<br />

<strong>UG194</strong>_5_02_032406<br />

Figure 5-3 shows a read transaction as defined by OP = 0b10. The addressed PHY device<br />

(with physical address PHYAD) takes control of the MDIO wire during the turnaround<br />

cycle and then returns the 16-bit word from the register at REGAD.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 117<br />

<strong>UG194</strong> (v1.10) February 14, 2011