Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

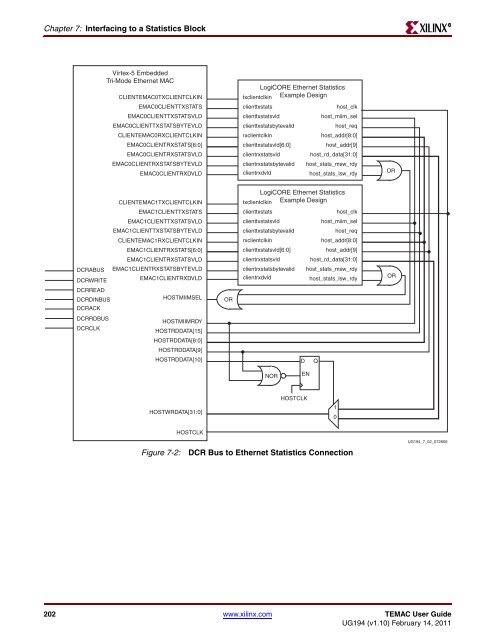

Chapter 7: Interfacing to a Statistics Block<br />

DCRABUS<br />

DCRWRITE<br />

DCRREAD<br />

DCRDINBUS<br />

DCRACK<br />

DCRRDBUS<br />

DCRCLK<br />

<strong>Virtex</strong>-5 <strong>Embedded</strong><br />

<strong>Tri</strong>-<strong>Mode</strong> <strong>Ethernet</strong> <strong>MAC</strong><br />

CLIENTE<strong>MAC</strong>0TXCLIENTCLKIN<br />

E<strong>MAC</strong>0CLIENTTXSTATS<br />

E<strong>MAC</strong>0CLIENTTXSTATSVLD<br />

E<strong>MAC</strong>0CLIENTTXSTATSBYTEVLD<br />

CLIENTE<strong>MAC</strong>0RXCLIENTCLKIN<br />

E<strong>MAC</strong>0CLIENTRXSTATS[6:0]<br />

E<strong>MAC</strong>0CLIENTRXSTATSVLD<br />

E<strong>MAC</strong>0CLIENTRXSTATSBYTEVLD<br />

E<strong>MAC</strong>0CLIENTRXDVLD<br />

CLIENTE<strong>MAC</strong>1TXCLIENTCLKIN<br />

E<strong>MAC</strong>1CLIENTTXSTATS<br />

E<strong>MAC</strong>1CLIENTTXSTATSVLD<br />

E<strong>MAC</strong>1CLIENTTXSTATSBYTEVLD<br />

CLIENTE<strong>MAC</strong>1RXCLIENTCLKIN<br />

E<strong>MAC</strong>1CLIENTRXSTATS[6:0]<br />

E<strong>MAC</strong>1CLIENTRXSTATSVLD<br />

E<strong>MAC</strong>1CLIENTRXSTATSBYTEVLD<br />

E<strong>MAC</strong>1CLIENTRXDVLD<br />

HOSTMIIMSEL<br />

HOSTMIIMRDY<br />

HOSTRDDATA[15]<br />

HOSTRDDATA[8:0]<br />

HOSTRDDATA[9]<br />

HOSTRDDATA[10]<br />

HOSTWRDATA[31:0]<br />

HOSTCLK<br />

OR<br />

LogiCORE <strong>Ethernet</strong> Statistics<br />

txclientclkin Example Design<br />

clienttxstats<br />

host_clk<br />

clienttxstatsvld<br />

host_miim_sel<br />

clienttxstatsbytevalid<br />

rxclientclkin<br />

clienttxstatsvld[6:0]<br />

clientrxstatsvld<br />

clientrxstatsbytevalid<br />

clientrxdvld<br />

host_req<br />

host_addr[8:0]<br />

host_addr[9]<br />

host_rd_data[31:0]<br />

LogiCORE <strong>Ethernet</strong> Statistics<br />

txclientclkin Example Design<br />

clienttxstats<br />

host_clk<br />

clienttxstatsvld<br />

host_miim_sel<br />

clienttxstatsbytevalid<br />

rxclientclkin<br />

clienttxstatsvld[6:0]<br />

clientrxstatsvld<br />

clientrxstatsbytevalid<br />

clientrxdvld<br />

host_stats_msw_rdy<br />

host_stats_lsw_rdy<br />

host_req<br />

host_addr[8:0]<br />

host_addr[9]<br />

host_rd_data[31:0]<br />

host_stats_msw_rdy<br />

host_stats_lsw_rdy<br />

Figure 7-2: DCR Bus to <strong>Ethernet</strong> Statistics Connection<br />

202 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

NOR<br />

D Q<br />

EN<br />

HOSTCLK<br />

1<br />

0<br />

OR<br />

OR<br />

<strong>UG194</strong>_7_02_072606<br />

R