Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 5: MDIO Interface<br />

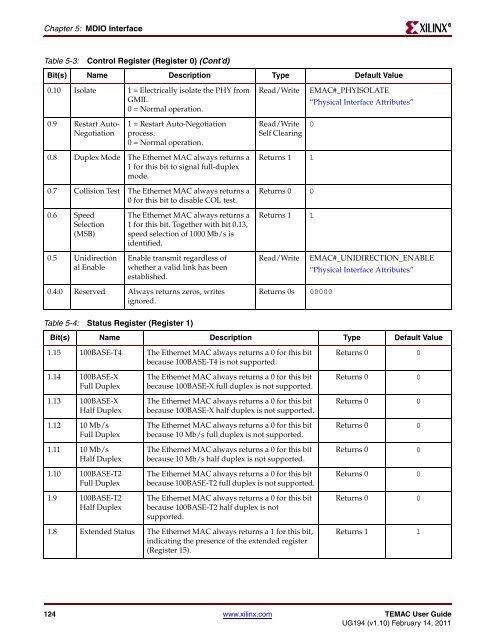

Table 5-3: Control Register (Register 0) (Cont’d)<br />

Bit(s) Name Description Type Default Value<br />

0.10 Isolate 1 = Electrically isolate the PHY from<br />

GMII.<br />

0 = Normal operation.<br />

0.9 Restart Auto-<br />

Negotiation<br />

1 = Restart Auto-Negotiation<br />

process.<br />

0 = Normal operation.<br />

0.8 Duplex <strong>Mode</strong> The <strong>Ethernet</strong> <strong>MAC</strong> always returns a<br />

1 for this bit to signal full-duplex<br />

mode.<br />

0.7 Collision Test The <strong>Ethernet</strong> <strong>MAC</strong> always returns a<br />

0 for this bit to disable COL test.<br />

0.6 Speed<br />

Selection<br />

(MSB)<br />

0.5 Unidirection<br />

al Enable<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a<br />

1 for this bit. Together with bit 0.13,<br />

speed selection of 1000 Mb/s is<br />

identified.<br />

Enable transmit regardless of<br />

whether a valid link has been<br />

established.<br />

0.4:0 Reserved Always returns zeros, writes<br />

ignored.<br />

Table 5-4: Status Register (Register 1)<br />

Read/Write E<strong>MAC</strong>#_PHYISOLATE<br />

“Physical Interface Attributes”<br />

Read/Write<br />

Self Clearing<br />

124 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

0<br />

Returns 1 1<br />

Returns 0 0<br />

Returns 1 1<br />

Read/Write E<strong>MAC</strong>#_UNIDIRECTION_ENABLE<br />

“Physical Interface Attributes”<br />

Returns 0s 00000<br />

Bit(s) Name Description Type Default Value<br />

1.15 100BASE-T4 The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 100BASE-T4 is not supported.<br />

1.14 100BASE-X<br />

Full Duplex<br />

1.13 100BASE-X<br />

Half Duplex<br />

1.12 10 Mb/s<br />

Full Duplex<br />

1.11 10 Mb/s<br />

Half Duplex<br />

1.10 100BASE-T2<br />

Full Duplex<br />

1.9 100BASE-T2<br />

Half Duplex<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 100BASE-X full duplex is not supported.<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 100BASE-X half duplex is not supported.<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 10 Mb/s full duplex is not supported.<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 10 Mb/s half duplex is not supported.<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 100BASE-T2 full duplex is not supported.<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 100BASE-T2 half duplex is not<br />

supported.<br />

1.8 Extended Status The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 1 for this bit,<br />

indicating the presence of the extended register<br />

(Register 15).<br />

Returns 0 0<br />

Returns 0 0<br />

Returns 0 0<br />

Returns 0 0<br />

Returns 0 0<br />

Returns 0 0<br />

Returns 0 0<br />

Returns 1 1<br />

R