Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 5: MDIO Interface<br />

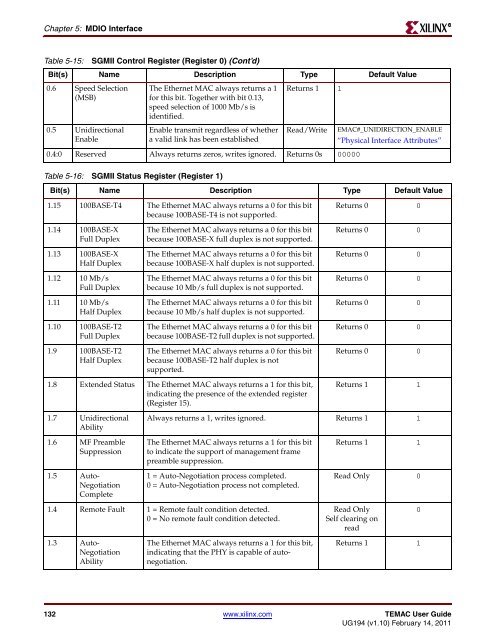

Table 5-15: SGMII Control Register (Register 0) (Cont’d)<br />

Bit(s) Name Description Type Default Value<br />

0.6 Speed Selection<br />

(MSB)<br />

0.5 Unidirectional<br />

Enable<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 1<br />

for this bit. Together with bit 0.13,<br />

speed selection of 1000 Mb/s is<br />

identified.<br />

Enable transmit regardless of whether<br />

a valid link has been established<br />

Returns 1 1<br />

0.4:0 Reserved Always returns zeros, writes ignored. Returns 0s 00000<br />

Table 5-16: SGMII Status Register (Register 1)<br />

Read/Write E<strong>MAC</strong>#_UNIDIRECTION_ENABLE<br />

“Physical Interface Attributes”<br />

Bit(s) Name Description Type Default Value<br />

1.15 100BASE-T4 The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 100BASE-T4 is not supported.<br />

1.14 100BASE-X<br />

Full Duplex<br />

1.13 100BASE-X<br />

Half Duplex<br />

1.12 10 Mb/s<br />

Full Duplex<br />

1.11 10 Mb/s<br />

Half Duplex<br />

1.10 100BASE-T2<br />

Full Duplex<br />

1.9 100BASE-T2<br />

Half Duplex<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 100BASE-X full duplex is not supported.<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 100BASE-X half duplex is not supported.<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 10 Mb/s full duplex is not supported.<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 10 Mb/s half duplex is not supported.<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 100BASE-T2 full duplex is not supported.<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 0 for this bit<br />

because 100BASE-T2 half duplex is not<br />

supported.<br />

1.8 Extended Status The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 1 for this bit,<br />

indicating the presence of the extended register<br />

(Register 15).<br />

1.7 Unidirectional<br />

Ability<br />

1.6 MF Preamble<br />

Suppression<br />

1.5 Auto-<br />

Negotiation<br />

Complete<br />

Returns 0 0<br />

Returns 0 0<br />

Returns 0 0<br />

Returns 0 0<br />

Returns 0 0<br />

Returns 0 0<br />

Returns 0 0<br />

Returns 1 1<br />

Always returns a 1, writes ignored. Returns 1 1<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 1 for this bit<br />

to indicate the support of management frame<br />

preamble suppression.<br />

1 = Auto-Negotiation process completed.<br />

0 = Auto-Negotiation process not completed.<br />

1.4 Remote Fault 1 = Remote fault condition detected.<br />

0 = No remote fault condition detected.<br />

1.3 Auto-<br />

Negotiation<br />

Ability<br />

The <strong>Ethernet</strong> <strong>MAC</strong> always returns a 1 for this bit,<br />

indicating that the PHY is capable of autonegotiation.<br />

Returns 1 1<br />

Read Only 0<br />

Read Only<br />

Self clearing on<br />

read<br />

132 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

0<br />

Returns 1 1<br />

R