Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 5: MDIO Interface<br />

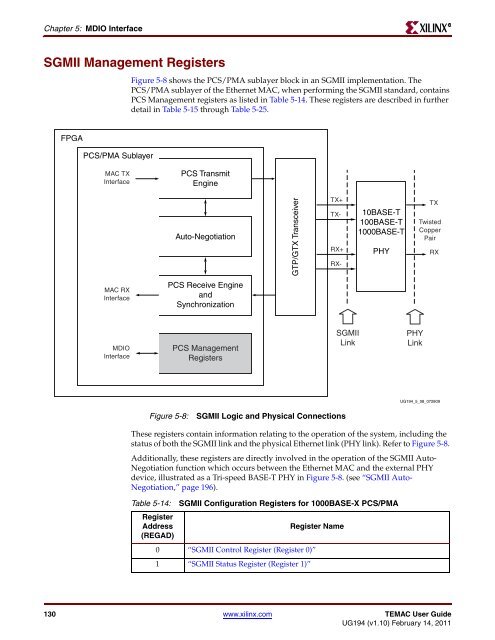

SGMII Management Registers<br />

<strong>FPGA</strong><br />

PCS/PMA Sublayer<br />

<strong>MAC</strong> TX<br />

Interface<br />

<strong>MAC</strong> RX<br />

Interface<br />

MDIO<br />

Interface<br />

Figure 5-8 shows the PCS/PMA sublayer block in an SGMII implementation. The<br />

PCS/PMA sublayer of the <strong>Ethernet</strong> <strong>MAC</strong>, when performing the SGMII standard, contains<br />

PCS Management registers as listed in Table 5-14. These registers are described in further<br />

detail in Table 5-15 through Table 5-25.<br />

PCS Transmit<br />

Engine<br />

Auto-Negotiation<br />

PCS Receive Engine<br />

and<br />

Synchronization<br />

PCS Management<br />

Registers<br />

Figure 5-8: SGMII Logic and Physical Connections<br />

10BASE-T<br />

100BASE-T<br />

1000BASE-T<br />

<strong>UG194</strong>_5_08_072809<br />

These registers contain information relating to the operation of the system, including the<br />

status of both the SGMII link and the physical <strong>Ethernet</strong> link (PHY link). Refer to Figure 5-8.<br />

Additionally, these registers are directly involved in the operation of the SGMII Auto-<br />

Negotiation function which occurs between the <strong>Ethernet</strong> <strong>MAC</strong> and the external PHY<br />

device, illustrated as a <strong>Tri</strong>-speed BASE-T PHY in Figure 5-8. (see “SGMII Auto-<br />

Negotiation,” page 196).<br />

130 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

GTP/GTX Transceiver<br />

TX+<br />

TX-<br />

RX+<br />

RX-<br />

SGMII<br />

Link<br />

PHY<br />

Table 5-14: SGMII Configuration Registers for 1000BASE-X PCS/PMA<br />

Register<br />

Address<br />

(REGAD)<br />

0 “SGMII Control Register (Register 0)”<br />

1 “SGMII Status Register (Register 1)”<br />

Register Name<br />

PHY<br />

Link<br />

TX<br />

Twisted<br />

Copper<br />

Pair<br />

RX<br />

R