Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 2: <strong>Ethernet</strong> <strong>MAC</strong> Overview<br />

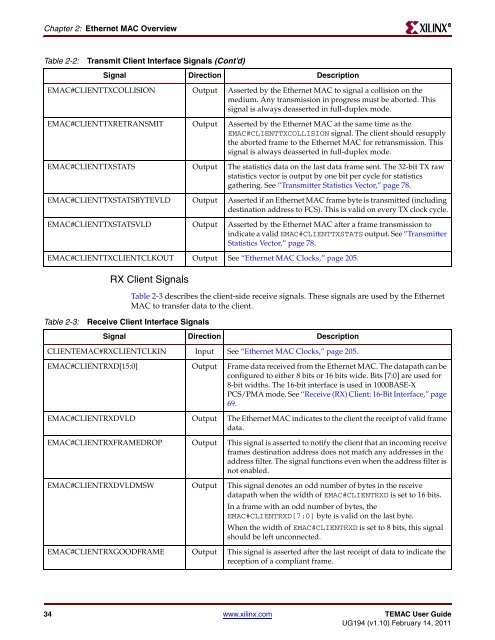

Table 2-2: Transmit Client Interface Signals (Cont’d)<br />

Signal Direction Description<br />

E<strong>MAC</strong>#CLIENTTXCOLLISION Output Asserted by the <strong>Ethernet</strong> <strong>MAC</strong> to signal a collision on the<br />

medium. Any transmission in progress must be aborted. This<br />

signal is always deasserted in full-duplex mode.<br />

E<strong>MAC</strong>#CLIENTTXRETRANSMIT Output Asserted by the <strong>Ethernet</strong> <strong>MAC</strong> at the same time as the<br />

E<strong>MAC</strong>#CLIENTTXCOLLISION signal. The client should resupply<br />

the aborted frame to the <strong>Ethernet</strong> <strong>MAC</strong> for retransmission. This<br />

signal is always deasserted in full-duplex mode.<br />

E<strong>MAC</strong>#CLIENTTXSTATS Output The statistics data on the last data frame sent. The 32-bit TX raw<br />

statistics vector is output by one bit per cycle for statistics<br />

gathering. See “Transmitter Statistics Vector,” page 78.<br />

E<strong>MAC</strong>#CLIENTTXSTATSBYTEVLD Output Asserted if an <strong>Ethernet</strong> <strong>MAC</strong> frame byte is transmitted (including<br />

destination address to FCS). This is valid on every TX clock cycle.<br />

E<strong>MAC</strong>#CLIENTTXSTATSVLD Output Asserted by the <strong>Ethernet</strong> <strong>MAC</strong> after a frame transmission to<br />

indicate a valid E<strong>MAC</strong>#CLIENTTXSTATS output. See “Transmitter<br />

Statistics Vector,” page 78.<br />

E<strong>MAC</strong>#CLIENTTXCLIENTCLKOUT Output See “<strong>Ethernet</strong> <strong>MAC</strong> Clocks,” page 205.<br />

RX Client Signals<br />

Table 2-3: Receive Client Interface Signals<br />

Table 2-3 describes the client-side receive signals. These signals are used by the <strong>Ethernet</strong><br />

<strong>MAC</strong> to transfer data to the client.<br />

Signal Direction Description<br />

CLIENTE<strong>MAC</strong>#RXCLIENTCLKIN Input See “<strong>Ethernet</strong> <strong>MAC</strong> Clocks,” page 205.<br />

E<strong>MAC</strong>#CLIENTRXD[15:0] Output Frame data received from the <strong>Ethernet</strong> <strong>MAC</strong>. The datapath can be<br />

configured to either 8 bits or 16 bits wide. Bits [7:0] are used for<br />

8-bit widths. The 16-bit interface is used in 1000BASE-X<br />

PCS/PMA mode. See “Receive (RX) Client: 16-Bit Interface,” page<br />

69.<br />

E<strong>MAC</strong>#CLIENTRXDVLD Output The <strong>Ethernet</strong> <strong>MAC</strong> indicates to the client the receipt of valid frame<br />

data.<br />

E<strong>MAC</strong>#CLIENTRXFRAMEDROP Output This signal is asserted to notify the client that an incoming receive<br />

frames destination address does not match any addresses in the<br />

address filter. The signal functions even when the address filter is<br />

not enabled.<br />

E<strong>MAC</strong>#CLIENTRXDVLDMSW Output This signal denotes an odd number of bytes in the receive<br />

datapath when the width of E<strong>MAC</strong>#CLIENTRXD is set to 16 bits.<br />

In a frame with an odd number of bytes, the<br />

E<strong>MAC</strong>#CLIENTRXD[7:0] byte is valid on the last byte.<br />

When the width of E<strong>MAC</strong>#CLIENTRXD is set to 8 bits, this signal<br />

should be left unconnected.<br />

E<strong>MAC</strong>#CLIENTRXGOODFRAME Output This signal is asserted after the last receipt of data to indicate the<br />

reception of a compliant frame.<br />

34 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

R