Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 2: <strong>Ethernet</strong> <strong>MAC</strong> Overview<br />

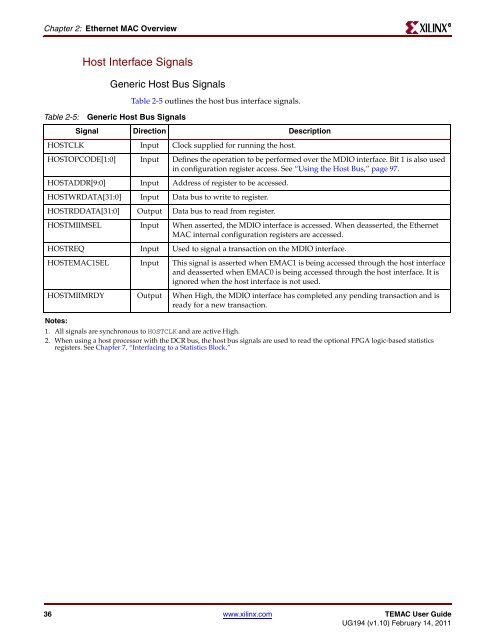

Host Interface Signals<br />

Generic Host Bus Signals<br />

Table 2-5: Generic Host Bus Signals<br />

Table 2-5 outlines the host bus interface signals.<br />

Signal Direction Description<br />

HOSTCLK Input Clock supplied for running the host.<br />

HOSTOPCODE[1:0] Input Defines the operation to be performed over the MDIO interface. Bit 1 is also used<br />

in configuration register access. See “Using the Host Bus,” page 97.<br />

HOSTADDR[9:0] Input Address of register to be accessed.<br />

HOSTWRDATA[31:0] Input Data bus to write to register.<br />

HOSTRDDATA[31:0] Output Data bus to read from register.<br />

HOSTMIIMSEL Input When asserted, the MDIO interface is accessed. When deasserted, the <strong>Ethernet</strong><br />

<strong>MAC</strong> internal configuration registers are accessed.<br />

HOSTREQ Input Used to signal a transaction on the MDIO interface.<br />

HOSTE<strong>MAC</strong>1SEL Input This signal is asserted when E<strong>MAC</strong>1 is being accessed through the host interface<br />

and deasserted when E<strong>MAC</strong>0 is being accessed through the host interface. It is<br />

ignored when the host interface is not used.<br />

HOSTMIIMRDY Output When High, the MDIO interface has completed any pending transaction and is<br />

ready for a new transaction.<br />

Notes:<br />

1. All signals are synchronous to HOSTCLK and are active High.<br />

2. When using a host processor with the DCR bus, the host bus signals are used to read the optional <strong>FPGA</strong> logic-based statistics<br />

registers. See Chapter 7, “Interfacing to a Statistics Block.”<br />

36 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

R