Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

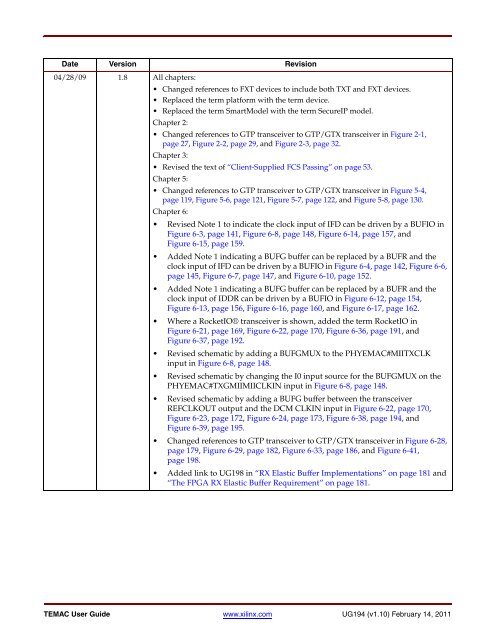

Date Version Revision<br />

04/28/09 1.8 All chapters:<br />

Changed references to FXT devices to include both TXT and FXT devices.<br />

Replaced the term platform with the term device.<br />

Replaced the term Smart<strong>Mode</strong>l with the term SecureIP model.<br />

Chapter 2:<br />

Changed references to GTP transceiver to GTP/GTX transceiver in Figure 2-1,<br />

page 27, Figure 2-2, page 29, and Figure 2-3, page 32.<br />

Chapter 3:<br />

Revised the text of “Client-Supplied FCS Passing” on page 53.<br />

Chapter 5:<br />

Changed references to GTP transceiver to GTP/GTX transceiver in Figure 5-4,<br />

page 119, Figure 5-6, page 121, Figure 5-7, page 122, and Figure 5-8, page 130.<br />

Chapter 6:<br />

Revised Note 1 to indicate the clock input of IFD can be driven by a BUFIO in<br />

Figure 6-3, page 141, Figure 6-8, page 148, Figure 6-14, page 157, and<br />

Figure 6-15, page 159.<br />

Added Note 1 indicating a BUFG buffer can be replaced by a BUFR and the<br />

clock input of IFD can be driven by a BUFIO in Figure 6-4, page 142, Figure 6-6,<br />

page 145, Figure 6-7, page 147, and Figure 6-10, page 152.<br />

Added Note 1 indicating a BUFG buffer can be replaced by a BUFR and the<br />

clock input of IDDR can be driven by a BUFIO in Figure 6-12, page 154,<br />

Figure 6-13, page 156, Figure 6-16, page 160, and Figure 6-17, page 162.<br />

Where a RocketIO® transceiver is shown, added the term RocketIO in<br />

Figure 6-21, page 169, Figure 6-22, page 170, Figure 6-36, page 191, and<br />

Figure 6-37, page 192.<br />

Revised schematic by adding a BUFGMUX to the PHYE<strong>MAC</strong>#MIITXCLK<br />

input in Figure 6-8, page 148.<br />

Revised schematic by changing the I0 input source for the BUFGMUX on the<br />

PHYE<strong>MAC</strong>#TXGMIIMIICLKIN input in Figure 6-8, page 148.<br />

Revised schematic by adding a BUFG buffer between the transceiver<br />

REFCLKOUT output and the DCM CLKIN input in Figure 6-22, page 170,<br />

Figure 6-23, page 172, Figure 6-24, page 173, Figure 6-38, page 194, and<br />

Figure 6-39, page 195.<br />

Changed references to GTP transceiver to GTP/GTX transceiver in Figure 6-28,<br />

page 179, Figure 6-29, page 182, Figure 6-33, page 186, and Figure 6-41,<br />

page 198.<br />

Added link to UG198 in “RX Elastic Buffer Implementations” on page 181 and<br />

“The <strong>FPGA</strong> RX Elastic Buffer Requirement” on page 181.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com <strong>UG194</strong> (v1.10) February 14, 2011