Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

R<br />

CLIENTE<strong>MAC</strong>#RXCLIENTCLKIN<br />

Flow Control Block<br />

Flow Control Block<br />

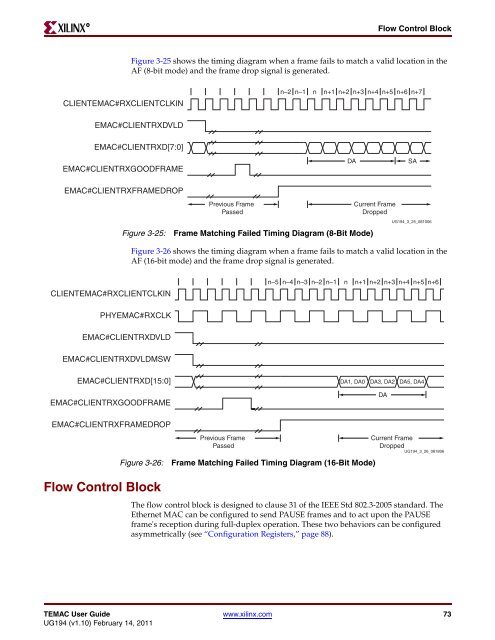

Figure 3-25 shows the timing diagram when a frame fails to match a valid location in the<br />

AF (8-bit mode) and the frame drop signal is generated.<br />

E<strong>MAC</strong>#CLIENTRXDVLD<br />

E<strong>MAC</strong>#CLIENTRXD[7:0]<br />

E<strong>MAC</strong>#CLIENTRXGOODFRAME<br />

E<strong>MAC</strong>#CLIENTRXFRAMEDROP<br />

CLIENTE<strong>MAC</strong>#RXCLIENTCLKIN<br />

Previous Frame<br />

Passed<br />

n–2 n–1 n n+1 n+2 n+3 n+4 n+5 n+6 n+7<br />

Figure 3-25: Frame Matching Failed Timing Diagram (8-Bit <strong>Mode</strong>)<br />

DA SA<br />

Current Frame<br />

Dropped<br />

<strong>UG194</strong>_3_25_081006<br />

Figure 3-26 shows the timing diagram when a frame fails to match a valid location in the<br />

AF (16-bit mode) and the frame drop signal is generated.<br />

PHYE<strong>MAC</strong>#RXCLK<br />

E<strong>MAC</strong>#CLIENTRXDVLD<br />

E<strong>MAC</strong>#CLIENTRXDVLDMSW<br />

E<strong>MAC</strong>#CLIENTRXD[15:0]<br />

E<strong>MAC</strong>#CLIENTRXGOODFRAME<br />

E<strong>MAC</strong>#CLIENTRXFRAMEDROP<br />

Previous Frame<br />

Passed<br />

n–5 n–4 n–3 n–2 n–1 n n+1 n+2 n+3 n+4 n+5 n+6<br />

Figure 3-26: Frame Matching Failed Timing Diagram (16-Bit <strong>Mode</strong>)<br />

DA1, DA0 DA3, DA2 DA5, DA4<br />

Current Frame<br />

Dropped<br />

The flow control block is designed to clause 31 of the IEEE Std 802.3-2005 standard. The<br />

<strong>Ethernet</strong> <strong>MAC</strong> can be configured to send PAUSE frames and to act upon the PAUSE<br />

frame's reception during full-duplex operation. These two behaviors can be configured<br />

asymmetrically (see “Configuration Registers,” page 88).<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 73<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

DA<br />

<strong>UG194</strong>_3_26_081806