Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

R<br />

Address Filtering<br />

Address Filtering<br />

The address filtering block accepts or rejects frames by examining the destination address<br />

of an incoming frame. This block includes:<br />

Matching of programmable unicast destination address<br />

Matching of four additional programmable general addresses<br />

Broadcast address recognition (0xFFFF_FFFF_FFFF)<br />

Optional pass-through mode with address filter disabled (promiscuous mode)<br />

Pause control frame address recognition (0x0100_00C2_8001)<br />

The Address Filter (AF) protects the client from extraneous traffic. With this technique, the<br />

hardware matches the Destination Address (DA) field of the <strong>Ethernet</strong> <strong>MAC</strong> frame. This<br />

relieves the task from the bus and software.<br />

The AF is programmed in software through the host interface. Pause-frame addresses and<br />

broadcast address are hardwired; they do not need to be programmed. The AF can be<br />

enabled and disabled under software control, using an enable bit in the control register. See<br />

“Address Filter Registers,” page 94 for the control register.<br />

When the function is enabled, <strong>Ethernet</strong> frames are passed to the client interface only if they<br />

pass the filter. When the AF function is disabled, all incoming RX frames are passed to the<br />

client interface.<br />

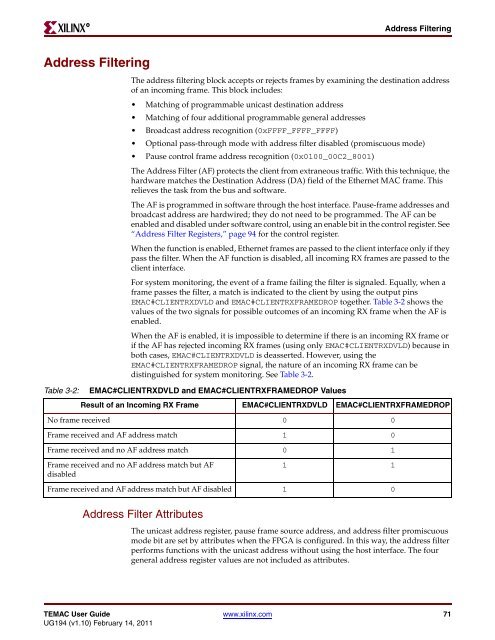

For system monitoring, the event of a frame failing the filter is signaled. Equally, when a<br />

frame passes the filter, a match is indicated to the client by using the output pins<br />

E<strong>MAC</strong>#CLIENTRXDVLD and E<strong>MAC</strong>#CLIENTRXFRAMEDROP together. Table 3-2 shows the<br />

values of the two signals for possible outcomes of an incoming RX frame when the AF is<br />

enabled.<br />

When the AF is enabled, it is impossible to determine if there is an incoming RX frame or<br />

if the AF has rejected incoming RX frames (using only E<strong>MAC</strong>#CLIENTRXDVLD) because in<br />

both cases, E<strong>MAC</strong>#CLIENTRXDVLD is deasserted. However, using the<br />

E<strong>MAC</strong>#CLIENTRXFRAMEDROP signal, the nature of an incoming RX frame can be<br />

distinguished for system monitoring. See Table 3-2.<br />

Table 3-2: E<strong>MAC</strong>#CLIENTRXDVLD and E<strong>MAC</strong>#CLIENTRXFRAMEDROP Values<br />

Result of an Incoming RX Frame E<strong>MAC</strong>#CLIENTRXDVLD E<strong>MAC</strong>#CLIENTRXFRAMEDROP<br />

No frame received 0 0<br />

Frame received and AF address match 1 0<br />

Frame received and no AF address match 0 1<br />

Frame received and no AF address match but AF<br />

disabled<br />

Address Filter Attributes<br />

1 1<br />

Frame received and AF address match but AF disabled 1 0<br />

The unicast address register, pause frame source address, and address filter promiscuous<br />

mode bit are set by attributes when the <strong>FPGA</strong> is configured. In this way, the address filter<br />

performs functions with the unicast address without using the host interface. The four<br />

general address register values are not included as attributes.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 71<br />

<strong>UG194</strong> (v1.10) February 14, 2011