Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

R<br />

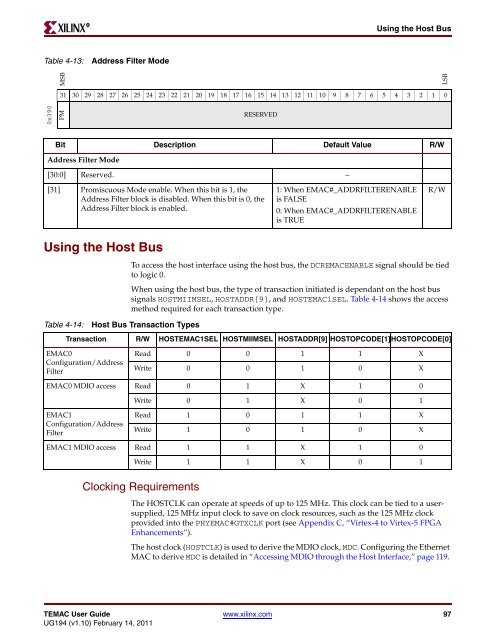

Table 4-13: Address Filter <strong>Mode</strong><br />

0x390<br />

MSB<br />

Using the Host Bus<br />

Using the Host Bus<br />

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0<br />

PM<br />

To access the host interface using the host bus, the DCRE<strong>MAC</strong>ENABLE signal should be tied<br />

to logic 0.<br />

When using the host bus, the type of transaction initiated is dependant on the host bus<br />

signals HOSTMIIMSEL, HOSTADDR[9], and HOSTE<strong>MAC</strong>1SEL. Table 4-14 shows the access<br />

method required for each transaction type.<br />

Clocking Requirements<br />

RESERVED<br />

Bit Description Default Value R/W<br />

Address Filter <strong>Mode</strong><br />

[30:0] Reserved. –<br />

[31] Promiscuous <strong>Mode</strong> enable. When this bit is 1, the<br />

Address Filter block is disabled. When this bit is 0, the<br />

Address Filter block is enabled.<br />

Table 4-14: Host Bus Transaction Types<br />

1: When E<strong>MAC</strong>#_ADDRFILTERENABLE<br />

is FALSE<br />

0: When E<strong>MAC</strong>#_ADDRFILTERENABLE<br />

is TRUE<br />

Transaction R/W HOSTE<strong>MAC</strong>1SEL HOSTMIIMSEL HOSTADDR[9] HOSTOPCODE[1]HOSTOPCODE[0]<br />

E<strong>MAC</strong>0<br />

Configuration/Address<br />

Filter<br />

Read 0 0 1 1 X<br />

Write 0 0 1 0 X<br />

E<strong>MAC</strong>0 MDIO access Read 0 1 X 1 0<br />

E<strong>MAC</strong>1<br />

Configuration/Address<br />

Filter<br />

Write 0 1 X 0 1<br />

Read 1 0 1 1 X<br />

Write 1 0 1 0 X<br />

E<strong>MAC</strong>1 MDIO access Read 1 1 X 1 0<br />

Write 1 1 X 0 1<br />

The HOSTCLK can operate at speeds of up to 125 MHz. This clock can be tied to a usersupplied,<br />

125 MHz input clock to save on clock resources, such as the 125 MHz clock<br />

provided into the PHYE<strong>MAC</strong>#GTXCLK port (see Appendix C, “<strong>Virtex</strong>-4 to <strong>Virtex</strong>-5 <strong>FPGA</strong><br />

Enhancements”).<br />

The host clock (HOSTCLK) is used to derive the MDIO clock, MDC. Configuring the <strong>Ethernet</strong><br />

<strong>MAC</strong> to derive MDC is detailed in “Accessing MDIO through the Host Interface,” page 119.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 97<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

LSB<br />

R/W