Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

HOSTCLK<br />

HOSTMIIMSEL<br />

HOSTREQ<br />

HOSTOPCODE[1:0]<br />

HOSTE<strong>MAC</strong>1SEL<br />

HOSTADDR[9:0]<br />

HOSTWRDATA[31:0]<br />

HOSTMIIMRDY<br />

HOSTRDDATA[31:0]<br />

DCRE<strong>MAC</strong>ENABLE<br />

DCRHOSTDONEIR<br />

R<br />

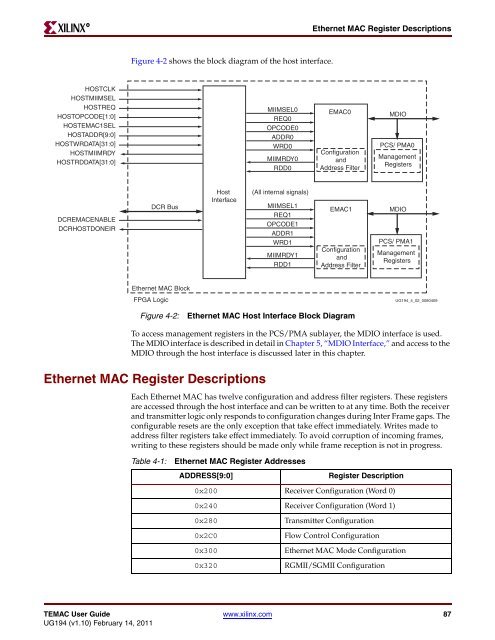

Figure 4-2 shows the block diagram of the host interface.<br />

DCR Bus<br />

<strong>Ethernet</strong> <strong>MAC</strong> Block<br />

<strong>FPGA</strong> Logic<br />

Host<br />

Interface<br />

Figure 4-2: <strong>Ethernet</strong> <strong>MAC</strong> Host Interface Block Diagram<br />

<strong>Ethernet</strong> <strong>MAC</strong> Register Descriptions<br />

To access management registers in the PCS/PMA sublayer, the MDIO interface is used.<br />

The MDIO interface is described in detail in Chapter 5, “MDIO Interface,” and access to the<br />

MDIO through the host interface is discussed later in this chapter.<br />

<strong>Ethernet</strong> <strong>MAC</strong> Register Descriptions<br />

MIIMSEL0<br />

REQ0<br />

OPCODE0<br />

ADDR0<br />

WRD0<br />

MIIMRDY0<br />

RDD0<br />

(All internal signals)<br />

MIIMSEL1<br />

REQ1<br />

OPCODE1<br />

ADDR1<br />

WRD1<br />

MIIMRDY1<br />

RDD1<br />

E<strong>MAC</strong>0<br />

E<strong>MAC</strong>1<br />

<strong>UG194</strong>_4_02_0080409<br />

Each <strong>Ethernet</strong> <strong>MAC</strong> has twelve configuration and address filter registers. These registers<br />

are accessed through the host interface and can be written to at any time. Both the receiver<br />

and transmitter logic only responds to configuration changes during Inter Frame gaps. The<br />

configurable resets are the only exception that take effect immediately. Writes made to<br />

address filter registers take effect immediately. To avoid corruption of incoming frames,<br />

writing to these registers should be made only while frame reception is not in progress.<br />

Table 4-1: <strong>Ethernet</strong> <strong>MAC</strong> Register Addresses<br />

Configuration<br />

and<br />

Address Filter<br />

Configuration<br />

and<br />

Address Filter<br />

PCS/ PMA0<br />

Management<br />

Registers<br />

PCS/ PMA1<br />

Management<br />

Registers<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 87<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

MDIO<br />

MDIO<br />

ADDRESS[9:0] Register Description<br />

0x200 Receiver Configuration (Word 0)<br />

0x240 Receiver Configuration (Word 1)<br />

0x280 Transmitter Configuration<br />

0x2C0 Flow Control Configuration<br />

0x300 <strong>Ethernet</strong> <strong>MAC</strong> <strong>Mode</strong> Configuration<br />

0x320 RGMII/SGMII Configuration