Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

R<br />

Table 3-3: Bit Definitions for the Transmitter Statistics Vector (Cont’d)<br />

TX_STATISTICS_VECTOR Name Description<br />

Receiver Statistics Vector<br />

Statistics Vectors<br />

4 CONTROL_FRAME Asserted if the previous frame has the special<br />

<strong>Ethernet</strong> <strong>MAC</strong> control type code 88-08 in the LT<br />

field.<br />

3 UNDERRUN_FRAME Asserted if the previous frame contains an underrun<br />

error.<br />

2 MULTICAST_FRAME Asserted if the previous frame contains a multicast<br />

address in the destination address field.<br />

1 BROADCAST_FRAME Asserted if the previous frame contains a broadcast<br />

address in the destination address field.<br />

0 SUCCESSFUL_FRAME Asserted if the previous frame is transmitted<br />

without error.<br />

Notes:<br />

1. Bits 28:20 of TX_STATISTICS_VECTOR are valid for half-duplex mode only.<br />

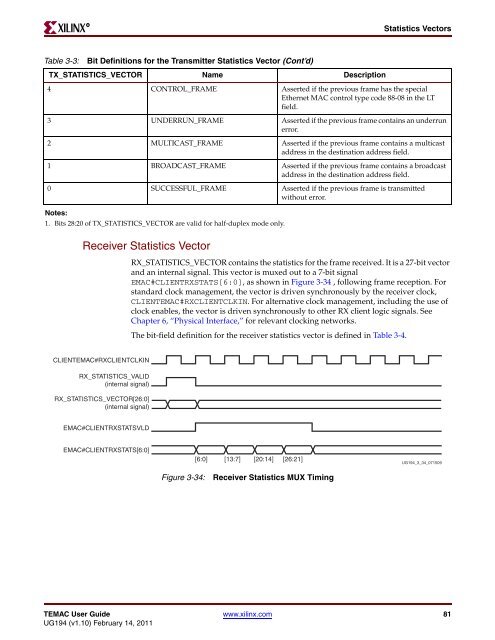

CLIENTE<strong>MAC</strong>#RXCLIENTCLKIN<br />

RX_STATISTICS_VALID<br />

(internal signal)<br />

RX_STATISTICS_VECTOR[26:0]<br />

(internal signal)<br />

E<strong>MAC</strong>#CLIENTRXSTATSVLD<br />

E<strong>MAC</strong>#CLIENTRXSTATS[6:0]<br />

RX_STATISTICS_VECTOR contains the statistics for the frame received. It is a 27-bit vector<br />

and an internal signal. This vector is muxed out to a 7-bit signal<br />

E<strong>MAC</strong>#CLIENTRXSTATS[6:0], as shown in Figure 3-34 , following frame reception. For<br />

standard clock management, the vector is driven synchronously by the receiver clock,<br />

CLIENTE<strong>MAC</strong>#RXCLIENTCLKIN. For alternative clock management, including the use of<br />

clock enables, the vector is driven synchronously to other RX client logic signals. See<br />

Chapter 6, “Physical Interface,” for relevant clocking networks.<br />

The bit-field definition for the receiver statistics vector is defined in Table 3-4.<br />

[6:0] [13:7] [20:14] [26:21]<br />

Figure 3-34: Receiver Statistics MUX Timing<br />

<strong>UG194</strong>_3_34_071509<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 81<br />

<strong>UG194</strong> (v1.10) February 14, 2011