Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

R<br />

Operation<br />

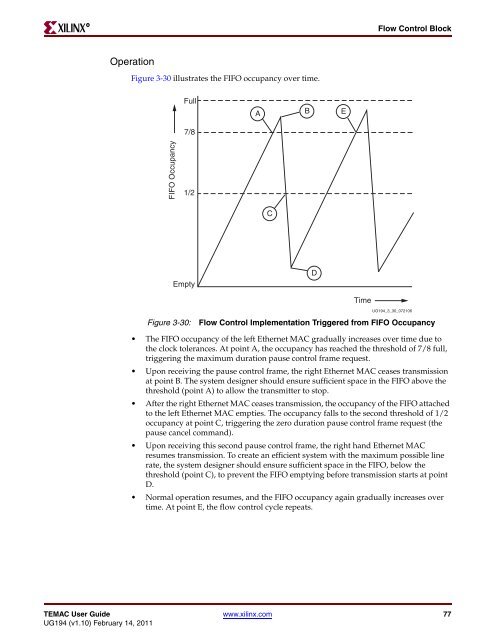

Figure 3-30 illustrates the FIFO occupancy over time.<br />

FIFO Occupancy<br />

Full<br />

7/8<br />

1/2<br />

Empty<br />

Flow Control Block<br />

Figure 3-30: Flow Control Implementation <strong>Tri</strong>ggered from FIFO Occupancy<br />

The FIFO occupancy of the left <strong>Ethernet</strong> <strong>MAC</strong> gradually increases over time due to<br />

the clock tolerances. At point A, the occupancy has reached the threshold of 7/8 full,<br />

triggering the maximum duration pause control frame request.<br />

Upon receiving the pause control frame, the right <strong>Ethernet</strong> <strong>MAC</strong> ceases transmission<br />

at point B. The system designer should ensure sufficient space in the FIFO above the<br />

threshold (point A) to allow the transmitter to stop.<br />

After the right <strong>Ethernet</strong> <strong>MAC</strong> ceases transmission, the occupancy of the FIFO attached<br />

to the left <strong>Ethernet</strong> <strong>MAC</strong> empties. The occupancy falls to the second threshold of 1/2<br />

occupancy at point C, triggering the zero duration pause control frame request (the<br />

pause cancel command).<br />

Upon receiving this second pause control frame, the right hand <strong>Ethernet</strong> <strong>MAC</strong><br />

resumes transmission. To create an efficient system with the maximum possible line<br />

rate, the system designer should ensure sufficient space in the FIFO, below the<br />

threshold (point C), to prevent the FIFO emptying before transmission starts at point<br />

D.<br />

Normal operation resumes, and the FIFO occupancy again gradually increases over<br />

time. At point E, the flow control cycle repeats.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 77<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

A<br />

C<br />

B<br />

D<br />

E<br />

Time<br />

<strong>UG194</strong>_3_30_072106