Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>FPGA</strong><br />

R<br />

PCS/PMA Sublayer<br />

<strong>MAC</strong> TX<br />

Interface<br />

<strong>MAC</strong> RX<br />

Interface<br />

MDIO<br />

Interface<br />

1000BASE-X PCS/PMA<br />

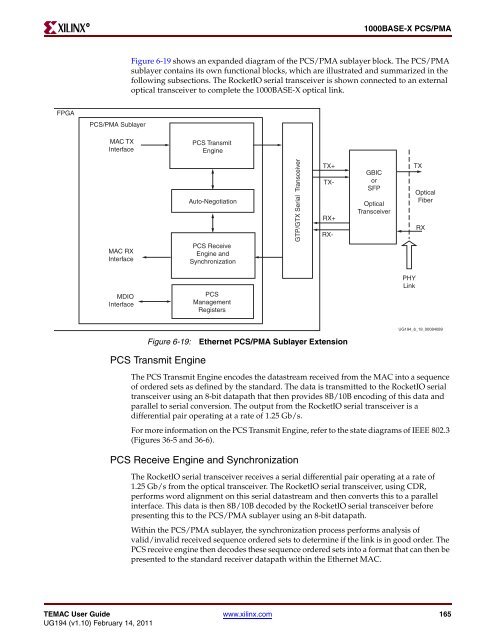

Figure 6-19 shows an expanded diagram of the PCS/PMA sublayer block. The PCS/PMA<br />

sublayer contains its own functional blocks, which are illustrated and summarized in the<br />

following subsections. The RocketIO serial transceiver is shown connected to an external<br />

optical transceiver to complete the 1000BASE-X optical link.<br />

Figure 6-19: <strong>Ethernet</strong> PCS/PMA Sublayer Extension<br />

PCS Transmit Engine<br />

PCS Transmit<br />

Engine<br />

Auto-Negotiation<br />

PCS Receive<br />

Engine and<br />

Synchronization<br />

PCS<br />

Management<br />

Registers<br />

The PCS Transmit Engine encodes the datastream received from the <strong>MAC</strong> into a sequence<br />

of ordered sets as defined by the standard. The data is transmitted to the RocketIO serial<br />

transceiver using an 8-bit datapath that then provides 8B/10B encoding of this data and<br />

parallel to serial conversion. The output from the RocketIO serial transceiver is a<br />

differential pair operating at a rate of 1.25 Gb/s.<br />

For more information on the PCS Transmit Engine, refer to the state diagrams of IEEE 802.3<br />

(Figures 36-5 and 36-6).<br />

PCS Receive Engine and Synchronization<br />

The RocketIO serial transceiver receives a serial differential pair operating at a rate of<br />

1.25 Gb/s from the optical transceiver. The RocketIO serial transceiver, using CDR,<br />

performs word alignment on this serial datastream and then converts this to a parallel<br />

interface. This data is then 8B/10B decoded by the RocketIO serial transceiver before<br />

presenting this to the PCS/PMA sublayer using an 8-bit datapath.<br />

Within the PCS/PMA sublayer, the synchronization process performs analysis of<br />

valid/invalid received sequence ordered sets to determine if the link is in good order. The<br />

PCS receive engine then decodes these sequence ordered sets into a format that can then be<br />

presented to the standard receiver datapath within the <strong>Ethernet</strong> <strong>MAC</strong>.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 165<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

GTP/GTX Serial Transceiver<br />

TX+<br />

TX-<br />

RX+<br />

RX-<br />

GBIC<br />

or<br />

SFP<br />

Optical<br />

Transceiver<br />

PHY<br />

Link<br />

TX<br />

Optical<br />

Fiber<br />

RX<br />

<strong>UG194</strong>_6_19_00084089