Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

R<br />

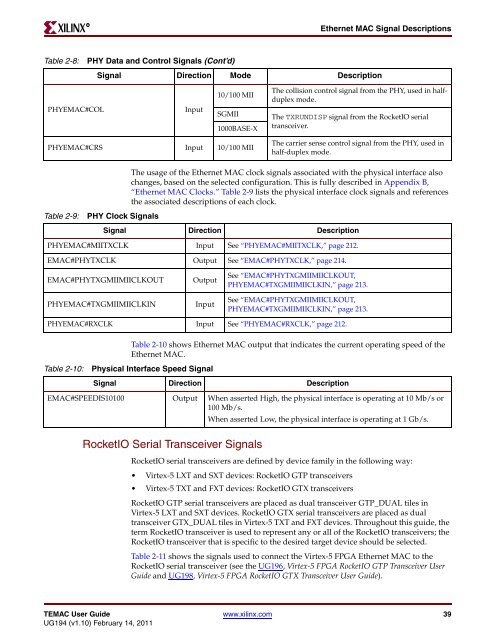

Table 2-8: PHY Data and Control Signals (Cont’d)<br />

Signal Direction <strong>Mode</strong> Description<br />

PHYE<strong>MAC</strong>#COL Input<br />

10/100 MII<br />

PHYE<strong>MAC</strong>#CRS Input 10/100 MII<br />

<strong>Ethernet</strong> <strong>MAC</strong> Signal Descriptions<br />

The usage of the <strong>Ethernet</strong> <strong>MAC</strong> clock signals associated with the physical interface also<br />

changes, based on the selected configuration. This is fully described in Appendix B,<br />

“<strong>Ethernet</strong> <strong>MAC</strong> Clocks.” Table 2-9 lists the physical interface clock signals and references<br />

the associated descriptions of each clock.<br />

Table 2-9: PHY Clock Signals<br />

Table 2-10 shows <strong>Ethernet</strong> <strong>MAC</strong> output that indicates the current operating speed of the<br />

<strong>Ethernet</strong> <strong>MAC</strong>.<br />

RocketIO Serial Transceiver Signals<br />

The collision control signal from the PHY, used in halfduplex<br />

mode.<br />

SGMII The TXRUNDISP signal from the RocketIO serial<br />

transceiver.<br />

1000BASE-X<br />

The carrier sense control signal from the PHY, used in<br />

half-duplex mode.<br />

Signal Direction Description<br />

PHYE<strong>MAC</strong>#MIITXCLK Input See “PHYE<strong>MAC</strong>#MIITXCLK,” page 212.<br />

E<strong>MAC</strong>#PHYTXCLK Output See “E<strong>MAC</strong>#PHYTXCLK,” page 214.<br />

E<strong>MAC</strong>#PHYTXGMIIMIICLKOUT Output<br />

PHYE<strong>MAC</strong>#TXGMIIMIICLKIN Input<br />

See “E<strong>MAC</strong>#PHYTXGMIIMIICLKOUT,<br />

PHYE<strong>MAC</strong>#TXGMIIMIICLKIN,” page 213.<br />

See “E<strong>MAC</strong>#PHYTXGMIIMIICLKOUT,<br />

PHYE<strong>MAC</strong>#TXGMIIMIICLKIN,” page 213.<br />

PHYE<strong>MAC</strong>#RXCLK Input See “PHYE<strong>MAC</strong>#RXCLK,” page 212.<br />

Table 2-10: Physical Interface Speed Signal<br />

Signal Direction Description<br />

E<strong>MAC</strong>#SPEEDIS10100 Output When asserted High, the physical interface is operating at 10 Mb/s or<br />

100 Mb/s.<br />

When asserted Low, the physical interface is operating at 1 Gb/s.<br />

RocketIO serial transceivers are defined by device family in the following way:<br />

<strong>Virtex</strong>-5 LXT and SXT devices: RocketIO GTP transceivers<br />

<strong>Virtex</strong>-5 TXT and FXT devices: RocketIO GTX transceivers<br />

RocketIO GTP serial transceivers are placed as dual transceiver GTP_DUAL tiles in<br />

<strong>Virtex</strong>-5 LXT and SXT devices. RocketIO GTX serial transceivers are placed as dual<br />

transceiver GTX_DUAL tiles in <strong>Virtex</strong>-5 TXT and FXT devices. Throughout this guide, the<br />

term RocketIO transceiver is used to represent any or all of the RocketIO transceivers; the<br />

RocketIO transceiver that is specific to the desired target device should be selected.<br />

Table 2-11 shows the signals used to connect the <strong>Virtex</strong>-5 <strong>FPGA</strong> <strong>Ethernet</strong> <strong>MAC</strong> to the<br />

RocketIO serial transceiver (see the UG196, <strong>Virtex</strong>-5 <strong>FPGA</strong> RocketIO GTP Transceiver User<br />

Guide and UG198, <strong>Virtex</strong>-5 <strong>FPGA</strong> RocketIO GTX Transceiver User Guide).<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 39<br />

<strong>UG194</strong> (v1.10) February 14, 2011