Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 3: Client Interface<br />

When the host interface is used, all the address filter registers are accessible by software,<br />

using either the DCR bus or the generic host bus. The attribute settings of the registers can<br />

be overridden by the software through the host interface. Also, the four general address<br />

registers are programmed through the host interface.<br />

Client RX Data/Control Interface<br />

CLIENTE<strong>MAC</strong>#RXCLIENTCLKIN<br />

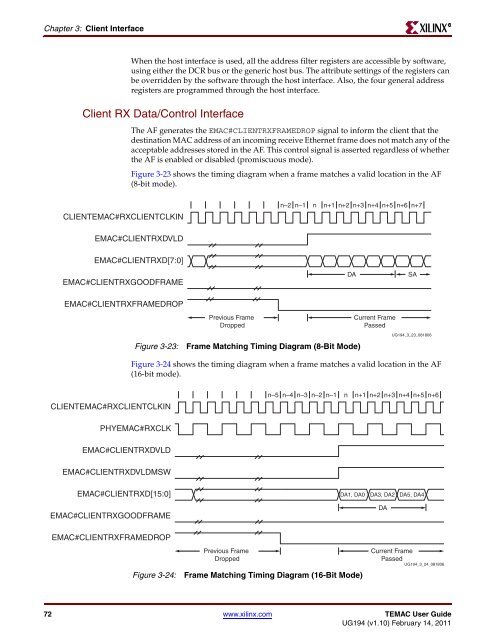

The AF generates the E<strong>MAC</strong>#CLIENTRXFRAMEDROP signal to inform the client that the<br />

destination <strong>MAC</strong> address of an incoming receive <strong>Ethernet</strong> frame does not match any of the<br />

acceptable addresses stored in the AF. This control signal is asserted regardless of whether<br />

the AF is enabled or disabled (promiscuous mode).<br />

Figure 3-23 shows the timing diagram when a frame matches a valid location in the AF<br />

(8-bit mode).<br />

E<strong>MAC</strong>#CLIENTRXDVLD<br />

E<strong>MAC</strong>#CLIENTRXD[7:0]<br />

E<strong>MAC</strong>#CLIENTRXGOODFRAME<br />

E<strong>MAC</strong>#CLIENTRXFRAMEDROP<br />

CLIENTE<strong>MAC</strong>#RXCLIENTCLKIN<br />

Previous Frame<br />

Dropped<br />

n–2 n–1 n n+1 n+2 n+3 n+4 n+5 n+6 n+7<br />

Figure 3-23: Frame Matching Timing Diagram (8-Bit <strong>Mode</strong>)<br />

DA SA<br />

Current Frame<br />

Passed<br />

<strong>UG194</strong>_3_23_081806<br />

Figure 3-24 shows the timing diagram when a frame matches a valid location in the AF<br />

(16-bit mode).<br />

PHYE<strong>MAC</strong>#RXCLK<br />

E<strong>MAC</strong>#CLIENTRXDVLD<br />

E<strong>MAC</strong>#CLIENTRXDVLDMSW<br />

E<strong>MAC</strong>#CLIENTRXD[15:0]<br />

E<strong>MAC</strong>#CLIENTRXGOODFRAME<br />

E<strong>MAC</strong>#CLIENTRXFRAMEDROP<br />

Previous Frame<br />

Dropped<br />

n–5 n–4 n–3 n–2 n–1 n n+1 n+2 n+3 n+4 n+5 n+6<br />

Figure 3-24: Frame Matching Timing Diagram (16-Bit <strong>Mode</strong>)<br />

DA1, DA0 DA3, DA2 DA5, DA4<br />

Current Frame<br />

Passed<br />

72 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

DA<br />

<strong>UG194</strong>_3_24_081806<br />

R