- Page 1 and 2:

UNIVERSIDAD COMPLUTENSE DE MADRID F

- Page 3 and 4:

Agradecimientos Es tradicional que

- Page 5 and 6:

« Las verdades más simples son aq

- Page 7 and 8:

Resumen Esta memoria afronta el pro

- Page 9 and 10:

2.5.6. Errores Graves: Single Event

- Page 11 and 12:

4.4.2.4 Consumo de corriente, corri

- Page 13 and 14:

7.7 Amplificadores de instrumentaci

- Page 15 and 16:

CAPITULO 1 INTRODUCCIÓN 1.1 Breve

- Page 17 and 18:

(a) (b) Fig. 1.3: Corte transversal

- Page 19 and 20:

5 Introducción Fig. 1.5: Dosis de

- Page 21 and 22:

7 Introducción uso en el sistema f

- Page 23 and 24:

9 Introducción simular la radiaci

- Page 25 and 26:

Capítulo 2 vacante y un átomo int

- Page 27 and 28:

Capítulo 2 Un mecanismo adicional

- Page 29 and 30:

Capítulo 2 D) Nivel de inyección

- Page 31 and 32:

Capítulo 2 Algunos autores utiliza

- Page 33 and 34:

Capítulo 2 a) Las colisiones de ne

- Page 35 and 36:

Capítulo 2 Insulator) son especial

- Page 37 and 38:

Capítulo 2 pero la radiación ioni

- Page 39 and 40:

Capítulo 2 Debido a la incertidumb

- Page 41 and 42:

Capítulo 2 Fig. 2.8: Dos transisto

- Page 43 and 44:

Capítulo 2 2.5.5. Errores Graves:

- Page 45 and 46:

Capítulo 2 Durante un tiempo, se s

- Page 47 and 48:

Capítulo 3 3) De película (Film r

- Page 49 and 50:

Capítulo 3 desplazamiento los afec

- Page 51 and 52:

Capítulo 3 Fig. 3.4: Las cargas po

- Page 53 and 54:

Capítulo 3 A) Difusión de portado

- Page 55 and 56:

Capítulo 3 ⎛ V ⎞ IS = IS0 ·ex

- Page 57 and 58:

Capítulo 3 ruptura se ha producido

- Page 59 and 60:

Capítulo 3 siendo IS,0 e IS,F las

- Page 61 and 62:

Capítulo 3 contacto se encuentra r

- Page 63 and 64:

Capítulo 3 consecuencia, se establ

- Page 65 and 66:

Capítulo 3 En cambio, este tipo de

- Page 67 and 68:

Capítulo 3 suma de dos componentes

- Page 69 and 70:

Capítulo 3 diodo real. La corrient

- Page 71 and 72:

Capítulo 3 V EA 2 WBq· NAB , = (3

- Page 73 and 74:

Capítulo 3 muestra la evolución d

- Page 75 and 76:

Capítulo 3 3.6.4 Efectos del la ra

- Page 77 and 78:

Capítulo 3 cargadas no son estáti

- Page 79 and 80:

Capítulo 3 En un transistor JFET d

- Page 81 and 82:

Capítulo 3 El objetivo primordial

- Page 83 and 84:

Capítulo 3 Fig. 3.25: Reducción d

- Page 85 and 86:

Capítulo 3 transistor se encuentra

- Page 87 and 88:

Capítulo 3 H· 2eNA ∆ VTH = ·

- Page 89 and 90:

Capítulo 3 cargas positivas e incl

- Page 91 and 92:

Capítulo 3 Fig. 3.33: Incremento d

- Page 93 and 94:

Capítulo 3 frecuencia y se dice qu

- Page 95 and 96:

Capítulo 4 Fig. 4.1: Símbolo del

- Page 97 and 98:

Capítulo 4 De acuerdo con esta nue

- Page 99 and 100:

Capítulo 4 minimizar la resistenci

- Page 101 and 102:

Capítulo 4 (a) (b) Fig. 4.5: Fuent

- Page 103 and 104: Capítulo 4 Wilson: I h + 2h I h +

- Page 105 and 106: Capítulo 4 corrientes que circulan

- Page 107 and 108: Capítulo 4 entrada o el rechazo de

- Page 109 and 110: Capítulo 4 VOUT = VIN−VBE, Q1

- Page 111 and 112: Capítulo 4 (a) (b) Fig. 4.17: Etap

- Page 113 and 114: Capítulo 4 Fig. 4.18 : Par bipolar

- Page 115 and 116: Capítulo 4 activa (p.e., eq. 3.12b

- Page 117 and 118: Capítulo 4 I f = I (4.34) u DSS π

- Page 119 and 120: Capítulo 4 salida y la entrada a l

- Page 121 and 122: Capítulo 4 Fig. 4.23 : Esquema pr

- Page 123 and 124: Capítulo 4 Tipo Tabla 4.2: Corrien

- Page 125 and 126: Capítulo 4 que esto ocurriría en

- Page 127 and 128: Capítulo 4 perfectamente apareadas

- Page 129 and 130: Capítulo 4 equivalente a afirmar q

- Page 131 and 132: Capítulo 4 Fig. 4.31: Amplificador

- Page 133 and 134: Capítulo 4 Puede observarse que cu

- Page 135 and 136: Capítulo 4 IB3,- ya que el amplifi

- Page 137 and 138: Capítulo 4 4.4.2.4 Consumo de corr

- Page 139 and 140: Capítulo 4 IShCC =+ VCCRCC (4.73)

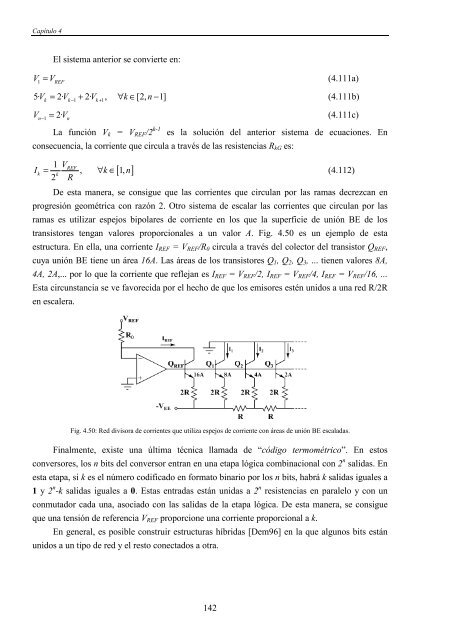

- Page 141 and 142: Capítulo 4 Se va a determinar la r

- Page 143 and 144: Capítulo 4 disminuiría y disminui

- Page 145 and 146: Capítulo 4 excepto una parte, estu

- Page 147 and 148: Capítulo 4 4.5.4.3 Influencia de l

- Page 149 and 150: Capítulo 4 4.5.5 Referencias de te

- Page 151 and 152: Capítulo 4 estar construida a part

- Page 153: Capítulo 4 a) Tensión mínima de

- Page 157 and 158: Capítulo 4 V k V =− ∑ b ·2 (4

- Page 159 and 160: Capítulo 4 n ( ) V11..11 = 2 − 1

- Page 161 and 162: CAPITULO 5 DESCRIPCIÓN DEL MONTAJE

- Page 163 and 164: Fig. 5.2: Espectro de energía del

- Page 165 and 166: Descripción del montaje experiment

- Page 167 and 168: Descripción del montaje experiment

- Page 169 and 170: Descripción del montaje experiment

- Page 171 and 172: Descripción del montaje experiment

- Page 173 and 174: Fig. 5.12: Estructura interna de la

- Page 175 and 176: Descripción del montaje experiment

- Page 177 and 178: CAPITULO 6 EFECTOS DE LA RADIACIÓN

- Page 179 and 180: Efectos de la radiación sobre ampl

- Page 181 and 182: Efectos de la radiación sobre ampl

- Page 183 and 184: Efectos de la radiación sobre ampl

- Page 185 and 186: Efectos de la radiación sobre ampl

- Page 187 and 188: Efectos de la radiación sobre ampl

- Page 189 and 190: Efectos de la radiación sobre ampl

- Page 191 and 192: Efectos de la radiación sobre ampl

- Page 193 and 194: Efectos de la radiación sobre ampl

- Page 195 and 196: Efectos de la radiación sobre ampl

- Page 197 and 198: Efectos de la radiación sobre ampl

- Page 199 and 200: Tabla 6.2: Relación entre el Slew

- Page 201 and 202: Efectos de la radiación sobre ampl

- Page 203 and 204: Efectos de la radiación sobre ampl

- Page 205 and 206:

Efectos de la radiación sobre ampl

- Page 207 and 208:

Efectos de la radiación sobre ampl

- Page 209 and 210:

Efectos de la radiación sobre ampl

- Page 211 and 212:

Efectos de la radiación sobre ampl

- Page 213 and 214:

CAPITULO 7 EFECTOS DE LA RADIACIÓN

- Page 215 and 216:

Efectos de la radiación sobre ampl

- Page 217 and 218:

Efectos de la radiación sobre ampl

- Page 219 and 220:

Efectos de la radiación sobre ampl

- Page 221 and 222:

Efectos de la radiación sobre ampl

- Page 223 and 224:

Efectos de la radiación sobre ampl

- Page 225 and 226:

Efectos de la radiación sobre ampl

- Page 227 and 228:

Efectos de la radiación sobre ampl

- Page 229 and 230:

Capítulo 8 Fig. 8.1: Relación ent

- Page 231 and 232:

Capítulo 8 modificado las caracter

- Page 233 and 234:

Capítulo 8 Fig. 8.7: Relación ent

- Page 235 and 236:

Capítulo 8 Fig. 8.10: Dependencia

- Page 237 and 238:

Capítulo 8 8.3.2 Tensión térmica

- Page 239 and 240:

Capítulo 8 En la zona de bajas ten

- Page 241 and 242:

Capítulo 8 De acuerdo con (4.82),

- Page 243 and 244:

Capítulo 8 Este último hecho just

- Page 245 and 246:

CAPITULO 9 EFECTOS DE LA RADIACIÓN

- Page 247 and 248:

237 Efectos de la radiación en con

- Page 249 and 250:

239 Efectos de la radiación en con

- Page 251 and 252:

241 Efectos de la radiación en con

- Page 253 and 254:

243 Efectos de la radiación en con

- Page 255 and 256:

245 Efectos de la radiación en con

- Page 257 and 258:

247 Efectos de la radiación en con

- Page 259 and 260:

c) Finalmente, el error de offset s

- Page 261 and 262:

251 Efectos de la radiación en con

- Page 263 and 264:

253 Efectos de la radiación en con

- Page 265 and 266:

Capítulo 10 las predicciones teór

- Page 267 and 268:

BIBLIOGRAFIA El criterio para ident

- Page 269 and 270:

261 Bibliografía Oxides after Heav

- Page 271 and 272:

263 Bibliografía of the IEEE Canad

- Page 273 and 274:

265 Bibliografía [Mau00] P. C. Mau

- Page 275 and 276:

267 Bibliografía [Sco89] J. H. Sco

- Page 277 and 278:

PUBLICACIONES RELACIONADAS A contin

- Page 279:

2004 271 Publicaciones Relacionadas