UNIVERSIDAD COMPLUTENSE DE MADRID

UNIVERSIDAD COMPLUTENSE DE MADRID

UNIVERSIDAD COMPLUTENSE DE MADRID

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Topologías internas de un amplificador operacional y dispositivos relacionados<br />

A diferencia de los errores de offset y de ganancia, este parámetro no puede ser corregido<br />

ni mediante material externo, como potenciómetros, ni mediante el uso de software apropiado.<br />

Asimismo, si se produce un cambio en la entrada, la salida no alcanza el nuevo estado hasta<br />

que no ha transcurrido una determinada cantidad de tiempo, llamado de asentamiento.<br />

En general, los errores de ganancia y los de no linealidad están relacionados con los valores<br />

exactos de las resistencias o transistores de la red del conversor. Por ejemplo, de (4.114) se<br />

deduce inmediatamente que, si RFB es ligeramente diferente de R, V11..11 ≠ (2 n -1)·VLSB, aparece un<br />

error de ganancia no nulo. Los errores de no linealidad surgen cuando las relaciones entre las<br />

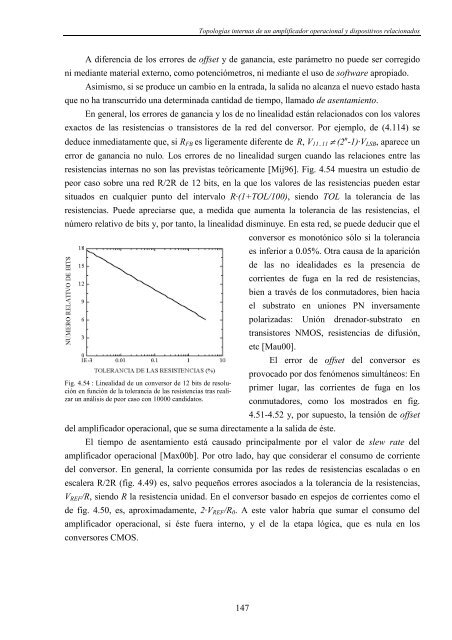

resistencias internas no son las previstas teóricamente [Mij96]. Fig. 4.54 muestra un estudio de<br />

peor caso sobre una red R/2R de 12 bits, en la que los valores de las resistencias pueden estar<br />

situados en cualquier punto del intervalo R·(1+TOL/100), siendo TOL la tolerancia de las<br />

resistencias. Puede apreciarse que, a medida que aumenta la tolerancia de las resistencias, el<br />

número relativo de bits y, por tanto, la linealidad disminuye. En esta red, se puede deducir que el<br />

conversor es monotónico sólo si la tolerancia<br />

es inferior a 0.05%. Otra causa de la aparición<br />

de las no idealidades es la presencia de<br />

corrientes de fuga en la red de resistencias,<br />

bien a través de los conmutadores, bien hacia<br />

el substrato en uniones PN inversamente<br />

polarizadas: Unión drenador-substrato en<br />

transistores NMOS, resistencias de difusión,<br />

etc [Mau00].<br />

El error de offset del conversor es<br />

provocado por dos fenómenos simultáneos: En<br />

primer lugar, las corrientes de fuga en los<br />

conmutadores, como los mostrados en fig.<br />

4.51-4.52 y, por supuesto, la tensión de offset<br />

del amplificador operacional, que se suma directamente a la salida de éste.<br />

El tiempo de asentamiento está causado principalmente por el valor de slew rate del<br />

amplificador operacional [Max00b]. Por otro lado, hay que considerar el consumo de corriente<br />

del conversor. En general, la corriente consumida por las redes de resistencias escaladas o en<br />

escalera R/2R (fig. 4.49) es, salvo pequeños errores asociados a la tolerancia de la resistencias,<br />

VREF/R, siendo R la resistencia unidad. En el conversor basado en espejos de corrientes como el<br />

de fig. 4.50, es, aproximadamente, 2·VREF/R0. A este valor habría que sumar el consumo del<br />

amplificador operacional, si éste fuera interno, y el de la etapa lógica, que es nula en los<br />

conversores CMOS.<br />

Fig. 4.54 : Linealidad de un conversor de 12 bits de resolución<br />

en función de la tolerancia de las resistencias tras realizar<br />

un análisis de peor caso con 10000 candidatos.<br />

147