- Page 1:

Test and MeasurementDivisionOperati

- Page 4 and 5:

Introduction on how to use the manu

- Page 7 and 8:

SMIQContentsContents1 Preparation f

- Page 9 and 10:

SMIQContents2.7.3.2 Preemphasis....

- Page 11 and 12:

SMIQContents2.15 Enhanced Functions

- Page 13 and 14:

SMIQContents2.29 Utilities.........

- Page 16 and 17:

ContentsSMIQ3.7.4 Application of th

- Page 18 and 19:

ContentsSMIQ5.3.9.2 AM Distortion .

- Page 20 and 21:

ContentsSMIQC Annex C..............

- Page 22 and 23:

ContentsSMIQFiguresFig. 1-1 SMIQ, v

- Page 24 and 25:

ContentsSMIQFig. 2-81 Menu DIGITAL

- Page 26 and 27:

ContentsSMIQFig. 2-168 DIGITAL STD

- Page 28 and 29:

ContentsSMIQFig. 2-244 Menu MEM SEQ

- Page 30 and 31:

Safety Instructions10. Ensure that

- Page 33 and 34:

1125.5555.03 1.1E-7SMIQPutting into

- Page 35 and 36:

1125.5555.03 1.3E-7SMIQFunctional T

- Page 37 and 38:

SMIQFitting the Options1.3.2 Overvi

- Page 39 and 40:

SMIQFitting the Options1.3.5 Option

- Page 41 and 42:

SMIQFitting the OptionsFitting the

- Page 43 and 44:

SMIQFitting the OptionsFitting the

- Page 45 and 46:

SMIQFitting the OptionsX606 X605 X6

- Page 47 and 48:

SMIQFitting the OptionsConnectorThe

- Page 49 and 50:

SMIQFront Panel2 Operation2.1 Front

- Page 51 and 52:

SMIQFront Panel2.1.2 Controls and I

- Page 53 and 54:

SMIQFront Panel2 DATA INPUTUnit key

- Page 55 and 56:

SMIQFront Panel3 MENU/VARIATIONRota

- Page 57 and 58:

SMIQFront Panel4QQInput external mo

- Page 59 and 60:

SMIQFront Panel7Brightness and cont

- Page 61 and 62:

SMIQRear Panel2.1.3 Elements of the

- Page 63 and 64:

SMIQRear Panel11PAR DATAPinDescript

- Page 65 and 66:

SMIQRear Panel12DATA DATA Cut-out,

- Page 67 and 68:

SMIQRear Panel15BER Interface for B

- Page 69 and 70:

SMIQRear Panel20RF RF Cut-out, prov

- Page 71 and 72:

SMIQBasic Operating StepsMenu field

- Page 73 and 74:

SMIQBasic Operating StepsQuick sele

- Page 75 and 76:

SMIQSample Setting for First Users2

- Page 77 and 78:

SMIQSample Setting for First UsersO

- Page 79 and 80:

SMIQSample Setting for First UsersO

- Page 81 and 82:

SMIQList EditorDELETE LISTFUNCTIONO

- Page 83 and 84:

SMIQList Editor2.2.11.3 Edition of

- Page 85 and 86:

SMIQList EditorFILL ATPARAMETERMEMO

- Page 87 and 88:

SMIQList EditorBlock function DELET

- Page 89 and 90:

SMIQList EditorOperating stepsExpla

- Page 91 and 92:

SMIQSave/Recall2.2.12 Save/Recall -

- Page 93 and 94:

SMIQRF Frequency2.4 RF FrequencyThe

- Page 95 and 96:

SMIQRF Level2.5 RF LevelThe RF leve

- Page 97 and 98:

SMIQRF LevelEXCLUDE FROM RCL OFF Th

- Page 99 and 100:

SMIQRF LevelMenu selection:LEVEL -

- Page 101 and 102:

SMIQRF LevelMenu selection:LEVEL -

- Page 103 and 104:

SMIQModulation - General2.6 Modulat

- Page 105 and 106:

SMIQModulation - General2.6.2 LF Ge

- Page 107 and 108:

SMIQAnalog Modulations2.7 Analog Mo

- Page 109 and 110:

SMIQAnalog Modulations2.7.3 Frequen

- Page 111 and 112:

SMIQAnalog Modulations2.7.4 Phase M

- Page 113 and 114:

SMIQAnalog Modulations2.7.5 Pulse M

- Page 115 and 116:

SMIQVector ModulationMenu selection

- Page 117 and 118:

SMIQVector Modulation2.8.1 I/Q Impa

- Page 119 and 120:

SMIQFading Simulation2.9.1 Output P

- Page 121 and 122:

SMIQFading Simulation2.9.4.1 Menu S

- Page 123 and 124:

SMIQFading SimulationPATHThe follow

- Page 125 and 126:

SMIQFading SimulationCORR PATHSwitc

- Page 127 and 128:

SMIQFading Simulation3GPP_BS_4.1.0_

- Page 129 and 130:

SMIQFading Simulation2.9.4.3 Menu M

- Page 131 and 132:

SMIQFading Simulation2.9.4.4 Menu B

- Page 133 and 134:

SMIQFading Simulation2.9.5 Test pro

- Page 135 and 136:

SMIQDigital Modulation2.10.1 Digita

- Page 137 and 138:

SMIQDigital Modulation2.10.1.3 FSK

- Page 139 and 140:

SMIQDigital ModulationDifferential

- Page 141 and 142:

SMIQDigital ModulationControl Lists

- Page 143 and 144:

SMIQDigital Modulation2.10.4 Digita

- Page 145 and 146:

SMIQDigital Modulation2.10.5.2 Exte

- Page 147 and 148:

SMIQDigital Modulation2.10.6 Envelo

- Page 149 and 150:

SMIQDigital Modulation2.10.9 Digita

- Page 151 and 152:

SMIQDigital Modulation(SOURCE... )

- Page 153 and 154:

SMIQDigital Modulation(MODULATION..

- Page 155 and 156:

SMIQDigital Modulation(FILTER...) F

- Page 157 and 158:

SMIQDigital ModulationTRIGGER MODES

- Page 159 and 160:

SMIQDigital Modulation(CLOCK...) CL

- Page 161 and 162:

SMIQDigital Modulation(POWER RAMPCO

- Page 163 and 164:

SMIQDigital Standard PHS2.11 Digita

- Page 165 and 166:

SMIQDigital Standard PHS2.11.2 PN G

- Page 167 and 168:

SMIQDigital Standard PHS2.11.5 Menu

- Page 169 and 170:

SMIQDigital Standard PHSFREQPHS100.

- Page 171 and 172:

SMIQDigital Standard PHSCLOCK...Ope

- Page 173 and 174:

SMIQDigital Standard PHSSLOT ATTENU

- Page 175 and 176:

SMIQDigital Standard PHS(SELECT SLO

- Page 177 and 178:

SMIQDigital Standard PHS(SELECT SLO

- Page 179 and 180:

SMIQDigital Standard IS-95 CDMATo g

- Page 181 and 182:

SMIQDigital Standard IS-95 CDMA2.12

- Page 183 and 184:

SMIQDigital Standard IS-95 CDMA2.12

- Page 185 and 186:

SMIQDigital Standard IS-95 CDMAMODE

- Page 187 and 188:

SMIQDigital Standard IS-95 CDMAREV

- Page 189 and 190:

SMIQDigital Standard IS-95 CDMA(TRI

- Page 191 and 192:

SMIQDigital Standard IS-95 CDMA(CLO

- Page 193 and 194:

SMIQDigital Standard IS-95 CDMA(SAV

- Page 195 and 196:

SMIQDigital Standard IS-95 CDMADATA

- Page 197 and 198:

SMIQDigital Standard IS-95 CDMACHAN

- Page 199 and 200:

SMIQ Digital Standard W-CDMA (NTT D

- Page 201 and 202:

SMIQ Digital Standard W-CDMA (NTT D

- Page 203 and 204:

SMIQ Digital Standard W-CDMA (NTT D

- Page 205 and 206:

SMIQ Digital Standard W-CDMA (NTT D

- Page 207 and 208:

SMIQ Digital Standard W-CDMA (NTT D

- Page 209 and 210:

SMIQ Digital Standard W-CDMA (NTT D

- Page 211 and 212:

SMIQ Digital Standard W-CDMA (NTT D

- Page 213 and 214:

SMIQ Digital Standard W-CDMA (NTT D

- Page 215 and 216:

SMIQ Digital Standard W-CDMA (NTT D

- Page 217 and 218:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 219 and 220:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 221 and 222:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 223 and 224:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 225 and 226:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 227 and 228:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 229 and 230:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 231 and 232:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 233 and 234:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 235 and 236:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 237 and 238:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 239 and 240:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 241 and 242:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 243 and 244:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 245 and 246:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 247 and 248:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 249 and 250:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 251 and 252:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 253 and 254:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 255 and 256:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 257 and 258:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 259 and 260:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 261 and 262:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 263 and 264:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 265 and 266:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 267 and 268:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 269 and 270:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 271 and 272:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 273 and 274:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 275 and 276:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 277 and 278:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 279 and 280:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 281 and 282:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 283 and 284:

SMIQDigital Standard 3GPP W-CDMA (F

- Page 285 and 286:

SMIQEnhanced Functions For Digital

- Page 287 and 288:

SMIQEnhanced Functions For Digital

- Page 289 and 290:

SMIQEnhanced Functions For Digital

- Page 291 and 292:

SMIQEnhanced Functions For Digital

- Page 293 and 294:

SMIQEnhanced Functions For Digital

- Page 295 and 296:

SMIQEnhanced Functions For Digital

- Page 297 and 298:

SMIQEnhanced Functions For Digital

- Page 299 and 300:

SMIQEnhanced Functions For Digital

- Page 301 and 302:

SMIQEnhanced Functions For Digital

- Page 303 and 304:

SMIQEnhanced Functions For Digital

- Page 305 and 306:

SMIQEnhanced Functions For Digital

- Page 307 and 308:

SMIQEnhanced Functions For Digital

- Page 309 and 310:

SMIQEnhanced Functions For Digital

- Page 311 and 312:

SMIQDigital Standard NADC2.16.1 Syn

- Page 313 and 314:

SMIQDigital Standard NADC2.16.3 Lis

- Page 315 and 316:

SMIQDigital Standard NADC(MODULATIO

- Page 317 and 318:

SMIQDigital Standard NADC(TRIGGER..

- Page 319 and 320:

SMIQDigital Standard NADC(POWER RAM

- Page 321 and 322:

SMIQDigital Standard NADCRATECONFIG

- Page 323 and 324:

SMIQDigital Standard NADC(SELECT SL

- Page 325 and 326:

SMIQDigital Standard NADC(SELECT SL

- Page 327 and 328:

SMIQDigital Standard PDC2.17 Digita

- Page 329 and 330:

SMIQDigital Standard PDC2.17.2 PN G

- Page 331 and 332:

SMIQDigital Standard PDC2.17.5 Menu

- Page 333 and 334:

SMIQDigital Standard PDCEXECUTETRIG

- Page 335 and 336:

SMIQDigital Standard PDC(CLOCK...)

- Page 337 and 338:

SMIQDigital Standard PDCFREQPHS100.

- Page 339 and 340:

SMIQDigital Standard PDC(SELECT SLO

- Page 341 and 342:

SMIQDigital Standard PDC(SELECT SLO

- Page 343 and 344:

SMIQDigital Standard PDC(SELECT SLO

- Page 345 and 346:

SMIQDigital Standard PDC(SELECT SLO

- Page 347 and 348:

SMIQDigital Standard PDC(SELECT SLO

- Page 349 and 350:

SMIQDigital Standard GSM/EDGE2.18 D

- Page 351 and 352:

SMIQDigital Standard GSM/EDGE2.18.2

- Page 353 and 354:

SMIQDigital Standard GSM/EDGE2.18.5

- Page 355 and 356:

SMIQDigital Standard GSM/EDGEEXECUT

- Page 357 and 358:

SMIQDigital Standard GSM/EDGEFig. 2

- Page 359 and 360:

SMIQDigital Standard GSM/EDGE(SAVE/

- Page 361 and 362:

SMIQDigital Standard GSM/EDGE(SELEC

- Page 363 and 364:

SMIQDigital Standard GSM/EDGEMenu s

- Page 365 and 366:

SMIQDigital Standard GSM/EDGE(SELEC

- Page 367 and 368:

SMIQDigital Standard DECT2.19.1 Syn

- Page 369 and 370:

SMIQDigital Standard DECT2.19.3 Lis

- Page 371 and 372:

SMIQDigital Standard DECT(MODULATIO

- Page 373 and 374:

SMIQDigital Standard DECT(TRIGGER..

- Page 375 and 376:

SMIQDigital Standard DECTPOWER RAMP

- Page 377 and 378:

SMIQDigital Standard DECT(SAVE/RCL

- Page 379 and 380: SMIQDigital Standard DECT(SELECT SL

- Page 381 and 382: SMIQDigital Standard DECT(SELECT SL

- Page 383 and 384: SMIQDigital Standard GPSFor more de

- Page 385 and 386: SMIQDigital Standard GPSTRIGGER...E

- Page 387 and 388: SMIQDigital Standard GPSPATTERNDATA

- Page 389 and 390: SMIQArbitrary Waveform Generator AR

- Page 391 and 392: SMIQArbitrary Waveform Generator AR

- Page 393 and 394: SMIQArbitrary Waveform Generator AR

- Page 395 and 396: SMIQArbitrary Waveform Generator AR

- Page 397 and 398: SMIQArbitrary Waveform Generator AR

- Page 399 and 400: SMIQArbitrary Waveform Generator AR

- Page 401 and 402: SMIQArbitrary Waveform Generator AR

- Page 403 and 404: SMIQArbitrary Waveform Generator AR

- Page 405 and 406: SMIQExternal Modulation Source AMIQ

- Page 407 and 408: SMIQExternal Modulation Source AMIQ

- Page 409 and 410: SMIQExternal Modulation Source AMIQ

- Page 411 and 412: SMIQExternal Modulation Source AMIQ

- Page 413 and 414: SMIQExternal Modulation Source AMIQ

- Page 415 and 416: SMIQExternal Modulation Source AMIQ

- Page 417 and 418: SMIQBit Error Rate Test2.23.1 Bit E

- Page 419 and 420: SMIQBit Error Rate TestPRBSDATA POL

- Page 421 and 422: SMIQBit Error Rate Test2.23.1.2 Sig

- Page 423 and 424: SMIQBit Error Rate TestBER measurem

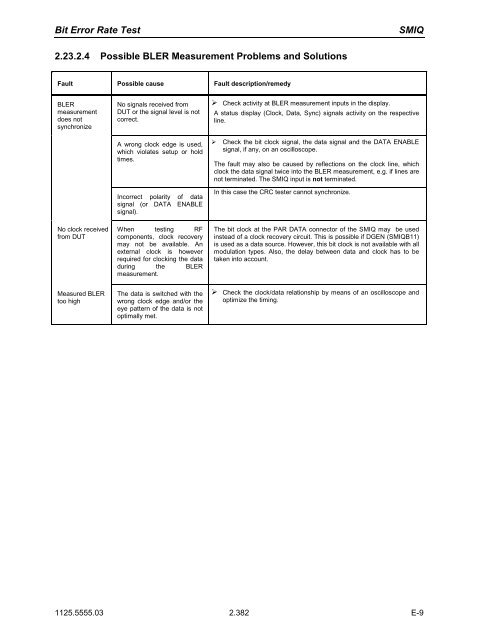

- Page 425 and 426: SMIQBit Error Rate TestPossible Pro

- Page 427 and 428: SMIQBit Error Rate TestSTATEMODEEXE

- Page 429: SMIQBit Error Rate Testreliable BLE

- Page 433 and 434: SMIQNoise Generator and Distortion

- Page 435 and 436: SMIQNoise Generator and Distortion

- Page 437 and 438: SMIQNoise Generator and Distortion

- Page 439 and 440: SMIQLF Output2.25 LF OutputThe inte

- Page 441 and 442: SMIQSweep2.26.2 Selecting the Sweep

- Page 443 and 444: SMIQSweepMARKERThis output becomes

- Page 445 and 446: SMIQSweepSTEP LIN (LOG)DWELLInput v

- Page 447 and 448: SMIQSweepRESET SWEEPSets the starti

- Page 449 and 450: SMIQLIST Mode2.27 LIST ModeA sequen

- Page 451 and 452: SMIQLIST ModeMARKER At the first st

- Page 453 and 454: SMIQLIST ModeThe second page of the

- Page 455 and 456: SMIQMemory SequenceOperating Modes

- Page 457 and 458: SMIQMemory SequenceThe second page

- Page 459 and 460: SMIQUtilities2.29.2 Parameter of th

- Page 461 and 462: SMIQUtilities2.29.4 Suppressing Ind

- Page 463 and 464: SMIQUtilitiesEXT FREQUENCYInput val

- Page 465 and 466: SMIQUtilities2.29.9 Calibration (CA

- Page 467 and 468: SMIQUtilitiesCalibration VECTOR MOD

- Page 469 and 470: SMIQUtilitiesCalibration ALC TABLEF

- Page 471 and 472: SMIQUtilitiesCalibration LFGENCalib

- Page 473 and 474: SMIQUtilities2.29.11 Voltage Indica

- Page 475 and 476: SMIQUtilities2.29.13 Indications of

- Page 477 and 478: SMIQUtilities2.29.16 Setting Auxili

- Page 479 and 480: SMIQUtilities2.29.18 Installation o

- Page 481:

SMIQError Messages2.32 Error Messag

- Page 484 and 485:

IndexSMIQvalue range ..............

- Page 486 and 487:

IndexSMIQDisplaybrightness.........

- Page 488 and 489:

IndexSMIQBIT CLOCK ................

- Page 490 and 491:

IndexSMIQadditional................

- Page 492 and 493:

IndexSMIQQAM modulation............

- Page 494 and 495:

IndexSMIQbroadband AM..............