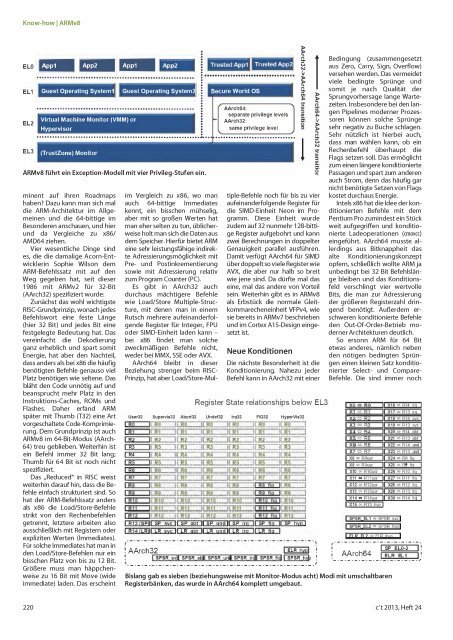

Know-how I ARMv8ELOEL 1EL2I__ _Guest Operati ng System1 IVirtual Machine Monitor (VMM) orHypervisorGuest Operating SystemIIure World OSAArch64:separate privilege IeveisAArch32:same privilege Ievei• • • •• • • •• •• • •• • • •• • • • • • • • • •• • • •• • • • •• • • • • • • • • • • • • • • •• •• • • • • • • • • -. • • • • • • •• • • ea • • • •• ••• •• • •• • • • • • • • • •EL3 I (Trustzone) MonitorARMv8 führt ein Exception-Modell mit vier Privileg-Stufen ein.minent auf ihren Roadmapshaben? Dazu kann man sich maldie ARM-Architektur im Allgemeinenund die 64-bittige imBesonderen anschauen, und hierund da Vergleiche zu x86/AMD64 ziehen.Vier wesentliche Dinge sindes, die die damalige Acorn-EntwicklerinSophie Wilson demARM-Befehlssatz mit auf denWeg gegeben hat, seit dieser1986 mit ARMv2 für 32-Bit(AArch32) spezifiziert wurde:Zunächst das wohl wichtigsteRISC-Grundprinzip, wonach jedesBefehlswort eine feste Länge(hier 32 Bit) und jedes Bit einefestgelegte Bedeutung hat. Dasvereinfacht die Dekodierungganz erheblich und spart somitEnergie, hat aber den Nachteil,dass anders als bei x86 die häufigbenötigten Befehle genauso vielPlatz benötigen wie seltene. Dasbläht den Code unnötig auf undbeansprucht mehr Platz in denInstruktions-Caches, ROMs undFlashes. Daher erfand ARMspäter mit Thumb (T32) eine Artvorgeschaltete Code-Komprimierung.Dem Grundprinzip ist auchARMv8 im 64-Bit-Modus (AArch-64) treu geblieben. Weiterhin istein Befehl immer 32 Bit lang;Thumb für 64 Bit ist noch nichtspezifiziert.Das "Reduced" in RISC weistweiterhin darauf hin, dass die Befehleeinfach strukturiert sind. Sohat der ARM-Befehlssatz andersals x86 die Load/Store-Befehlestrikt von den Rechenbefehlengetrennt, letztere arbeiten alsoausschließlich mit Registern oderexpliziten Werten (Immediates).Für solche Immediates hat man inden Load/Store-Befehlen nur einbisschen Platz von bis zu 12 Bit.Größere muss man häppchenweisezu 16 Bit mit Move (wideimmediate) laden. Das erscheintim Vergleich zu x86, wo manauch 64-bittige Immediateskennt, ein bisschen mühselig,aber mit so großen Werten hatman eher selten zu tun, üblicherweiseholt man sich die Daten ausdem Speicher. Hierfür bietet ARMeine sehr leistungsfähige indirekteAdressierungsmöglichkeit mitPre- und Postinkrementierungsowie mit Adressierung relativzum Program Counter (PC).Es gibt in AArch32 auchdurchaus mächtigere Befehlewie Load/Store Multiple-Structure,mit denen man in einemRutsch mehrere aufeinanderfolgendeRegister für Integer, FPUoder SIMD-Einheit laden kann -bei x86 findet man solchezweckmäßigen Befehle nicht,weder bei MMX, SSE oder AVX.AArch64 bleibt in dieserBeziehung strenger beim RISCPrinzip, hat aber Load/Store-Mul-I...n':1'..".,v...n':1'a>..,.::Ill>l>...n':1'a>..,.3: v0 ::Il>10':1'..".,......QJ::Iö'...tiple-Befehle noch für bis zu vieraufeinanderfolgende Register fürdie SIMD-Einheit Neon im Programm.Diese Einheit wurdezudem auf 32 nunmehr 128-bittigeRegister aufgebohrt und kannzwei Berechnungen in doppelterGenauigkeit parallel ausführen.Damit verfügt AArch64 für SIMDüber doppelt so viele Register wieAVX, die aber nur halb so breitwie jene sind. Da dürfte mal daseine, mal das andere von Vorteilsein. Weiterhin gibt es in ARMv8als Erbstück die normale GleitkommarecheneinheitVFPv4, wiesie bereits in ARMv7 beschriebenund im Cortex A 15-Design eingesetztist.Neue KonditionenDie nächste Besonderheit ist dieKonditionierung. Nahezu jederBefehl kann in AArch32 mit einerRegister State relationships below EL3User32 Supervis32 Abort32 Undef32 lrq32 FIQ32 HyperVis32so I C:äc:::J [:BQ':::::J[ac ::J[a[::::::cac :::Kac::Js 1 ICXr:::::J r:&r::::Jcär::::::cär :::::Jc&c:::JC:si::::::s2 ICßi:::::J Cßi::::J [Ri::::JCiü::::::iC:BZ:::::iCRi::::JB3 IC:::::.i [:B:::::.im:::::Ka:::::iCB::::::iCa::::JB4 I C4::::J [:4::::JCI{C :::J[B:4 ::=Ka4:::::KaC::Jss IC&s::::J ms:::::mr::::J[&:::::ic&:::::Jc:s:::::Js6 I CXC:::.i r:iiC::JC&C :::K&C:::iC&::::K&C::Js1 IC:BC:::J [:BC::J[RC::J[Rf:::::Kaf:::::Kaf::::JRB t:Bc:::.i [:BC:::Kac:::Kac::::l RB fi a ICa!l::::::B9 1 Cß2:::::J m2:::::K&C :::K&:::::il B9 tia IC&C::Js1o !Ciiiii::::mm:::J C&Id::::K&IC:: JI s1o tia IC:B:iii::::JB11 l (ifii::::.i [iiii:::J[RU::::K&Ii ::::i l B11 ng I[:B:Ii::::Js1 2 I CB:1E:::.i [:ßii:::::i Cäi.i ::::J[B:ii::::il s 12 ti a IC:Rii::::J813 ISPjl SP svc II SP abt II SP und II SP irq II SP fiq II SP hyp I814 ILBUI LB syc II LR abt II LB und II LB jra II LR fjg II eLR hypl AArch321I SPSR svl! SPSR ablt SPSR uiil SPSR ir41 SPSR ti4 I SPSR hyP · - · - · - · - · - · - · - · - · - · - · - · - · - · - · - · - · - · - · - · - · - · - · - · - · - · - ·'Bedingung (zusammengesetztaus Zero, Carry, Sign, Overflow)versehen werden. Das vermeidetviele bedingte Sprünge undsomit je nach Qualität derSprungvorhersage lange Wartezeiten.Insbesondere bei den langenPipelines moderner Prozessorenkönnen solche Sprüngesehr negativ zu Buche schlagen.Sehr nützlich ist hierbei auch,dass man wählen kann, ob einRechenbefehl überhaupt dieFlags setzen soll. Das ermöglichtzum einen längere konditioniertePassagen und spart zum anderenauch Strom, denn das häufig garnicht benötigte Setzen von Flagskostet durchaus Energie.lntels x86 hat die Idee der konditioniertenBefehle mit demPentium Pro zumindest ein Stückweit aufgegriffen und konditionierteLadeoperationen (cmovcc)eingeführt. AArch64 musste allerdingsaus Bitknappheit dasalte Konditionierungskonzeptopfern, schließlich wollte ARM jaunbedingt bei 32 Bit Befehlslängebleiben und das Konditionsfeldverschlingt vier wertvolleBits, die man zur Adressierungder größeren Registerzahl dringendbenötigt. Außerdem erschwerenkonditionierte Befehleden Out-Of-Order-Betrieb modernerArchitekturen deutlich.So ersonn ARM für 64 Bitetwas anderes, nämlich nebenden nötigen bedingten Sprüngeneinen kleinen Satz konditionierterSelect- und CompareBefehle. Die sind immer nochXO * ROX1 R1X2 R2X3 R3X4 R4xs R5X6 RSX7 R7X8

Know-how I ARMv8erheblich leistungsfähiger als diekonditionierten Ladeoperationenbei x86, können unter anderemteilweise auch gleich invertierenund inkrementieren.BankingDie vierte Uridee von ARM ist dasRegister-Banking. Schon die frühenARM-Prozessoren waren -im Vergleich zum spartanischen386er - recht luxuriös mit 1632-bittigen Allzweckregistern ausgestattet.Hinzu kamen nochspezielle Program Status Register.Und nicht nur das, für lnterrupts,Exceptions und Moduswechselzwischen User und Supervisorschaltete der Prozessorfür eine bestimmte Teilmengedes Registersatzes auf eine andereBank um. Die Vorteile etwa beilnterrupts liegen auf der Hand.Für hohe Echtzeitanforderungenkennt ARM einen Fast lnterruptMode (FIQ32), für den acht eigenegebankte Register zur Verfügungstehen. ln aller Regel kanndie Behandlungsroutine damitunverzüglich mit der lnterruptBehandlung loslegen.Bei x86 hingegen ist das mitunterein recht langwieriger Prozess.Hier muss man erst einmalabwarten, bis der möglicherweisegerade lang laufende Befehl aufdem zu unterbrechenden Prozessorbeendet ist, dann wird die lnterruptDescriptorTable (IDT) ausgelesenund ein Stack-Frame eingerichtet.Irgendwann bekommtdie in der IDT eingehängte Behandlungsroutinedie Kontrolle,doch sie muss sich für ihre Arbeiterst einmal Platz machen und allebenötigten Register auf den Stackretten. Dabei können Cache- undTLB-Misses auftreten, die die Gesamtlatenzauf viele 1 00 wennnicht gar auf 1 000 Prozessortakteausdehnen - ein Graus für jedeEchtzeitanforderung.Bei den anderen ARM-Betriebsmodiist es allerdings ähnlich.Auch hier muss die Behandlungsroutineebenfalls erst einmalRegister retten, denn die eigenenBänke beschränken sichauf zwei Prozessorregister, dieüblicherweise als Stack-Pointerund Link-Register vorbelegt sind,sowie auf zwei Status-Register.Insgesamt verfügt AArch32 mitdiesem gebankten Registerkonzeptüber 31 logische Prozessorregisterund 11 Status-Register.ARMv7 kennt darüber hinausnoch einen Monitor-Modus mitzwei weiteren Registern.Performance lmprovement vs. Cortex-A 15 (28nm)60% ,----• Cortex-A1 5(28nm)20%10%0%BrowsingSPECUnter AArch64 sieht das allesganz anders aus. Zunächst einmalersetzt ein für die Virtualisierungviel besser geeignetes vierstufigesRingkonzept die bis zuacht Betriebsmodi von AArch32.Ganze unten ist der Applikations-oder User-Modus (ELO).Darüber liegt der Modus für dasGast-Betriebssystem (EL 1 ). Demübergeordnet ist der HypervisorModus (EL2). Ganz oben wachtein TrustZone-Monitor (EL3).Fährt man ein Secure OS, könnenspezielle Trusted Apps mitdem TrustZone-Monitor in geschützterWeise korrespondieren.Im Non-Secure-Modus hältsich der TrustZone-Monitor ausdem Geschehen heraus, dieSicherheitsverantwortung trägtder untergeordnete Hypervisorauf EL2. Der Secure-Moduskennt indes keinen Hypervisor,hier kommt allein der TrustZoneMonitor auf EL3 zum Einsatz.Die erste Veröffentlichung derARMv8-Architektur umfasst nurdas sogenannte Applikationsprofil,gekennzeichnet mit einem angehängtem,A' als ARMv8-A. Danebenwird es wie beim VorgängerARMv7 später auch ein EchtzeitprofilARMv8-R geben, daseine für Echtzeitverarbeitungbesser geeignete Virtualisierungsowie weitere Besonderheitenbietet.Fast lnterruptsIm AArch64 von AMRv8-A gibtes jedenfalls keine Fast lnterruptsund keine gebanktenRegister mehr, dafür zahlreichelnterrupt-Kontrollregister unteranderem für eine 10-Virtualisie-StreamDhrystonerung, genau so, wie man es fürmoderne Serveraufgaben benötigt.Der Registersatz umfasst31 64-bittige Register, eins fehltbei der möglichen Kodierung:1111 b steht fix für Null. Register30 steht auch nicht wirklich zurVerfügung, es ist fest als LinkRegister vorbelegt Im AArch32-Betrieb mappt ARMv8 geschicktdie vorhandenen 31 Register aufalle dort benötigten Bank-Register(ohne Monitor Mode). Dieoberen Hälften der 64-Bit-Registerbleiben dabei ungenutzt.Neu sind ferner die eingebautenKrypto-Engines mit AES undSHA und natürlich auch der weitausgrößere Adressbereich, denman unter AArch64 ansprechenkann. Smartphones werdenmehr als 4 GByte derzeit nochnicht unbedingt brauchen, aberfür Server der nächsten Generation,selbst für kleine Mikroserver,ist das unabdingbar.64 physische Adressbits sindallerdings nicht wirklich nötig,ARM beschränkt sich wie der Mitbewerbauch auf 48 Bit, also auf256 Terabyte Adressraum. DieUmrechnung aus den von denApplikationen verwendeten virtuellenAdressen zu den physischenist bei dieser AArch64etwas einfacher gestrickt undsomit schneller als bei x86.Neben den üblicherweise verwendetenSeitengrößen von4 KByte kann man bei AArch64auch 64-KByte-Einträge verwenden,ein guter Kompromiss zwischenden oft zu kleinen 4 K undden mit 2/4 M zu großen Einträgender x86-Welt. Bei Adressbereichenvon bis zu 4 Terabytekommt man so bei 64-K-Seiten-Ein lustiger Performancevergleichauf ARMs Website:Prozentual zu was? Undwelcher der gefühlt 50 SPECBenchmarks ist gemeint,SPECMail etwa?tabeilen mit einem schnellenzweistufigen Zugriffsschema aus.AusblickSpät kommt ARM mit 64 Bit,mehr als 20 Jahre nach MIPS64oder DEC-Aipha, die beide bereits32 64-bittige Integer undGleitkommaregister boten, abervielleicht ist auch jetzt erst dieZeit wirklich reif für 64 Bit.AArch64 ist jedenfalls ein sehrneuer Prozessor, eine sehr weitgehendeÜberarbeitung desalten ARM-Designs, viel weitergehenderals die vergleichsweisegeringen Änderungen, die AMDbeim Aufstieg auf AMD64 eingebrachthat. Kein Registerbanking,keine konditionieren Standardbefehle,komplett neue Opcodes,keine acht Betriebsmodi,sondern ein Konzept aus vierRingen, das dem bei x86 so unähnlichnicht ist.Ja, es ist fast schon eine Artltanium, mit dem großen Unterschied,dass hier das SchlüsselFeature Kompatibilität zur bestehenden32-bittigen Software auchin Bezug auf Performance offenbarernst genommen wurde, woraufdie ersten Ergebnissen mitApples A7 schließen lassen. FürSmartphones und Tablets ist dasauch dringend geboten, bei Servernstartet man bei Null, hier istes durchaus denkbar, dass einigeLizenznehmer auf 32 Bit ganzverzichten, um Validierungskostenund Energie zu sparen.Genau in dieser Variabilität durchdie vielen Lizenznehmer dürftedie Stärke von ARM liegen, beiSmartphones und Tablet sowiesound mit recht guten Chancen beiden kleinen, energiesparendenServern. Und wenn man BroadcomsAnkündigung mit 3 GHzTakt und "Server-dass Performance"sieht, ahnt man, dass daeinige wohl bereits höhere Serversphärenanpeilen - Intel seigewarnt.Ende Oktober, leider erst nachRedaktionsschluss, tagt ARMsEntwickler-Konferenz Techcon<strong>2013</strong>, da wird man sicherlichnoch einiges mehr dazu erfahren.(as) c'l:<strong>c't</strong> <strong>2013</strong>, Heft <strong>24</strong>221

- Seite 3 und 4:

Der Beginn einer wunderbaren Freund

- Seite 5 und 6:

WORTMANN AG empfiehlt Windows 8 Pro

- Seite 8 und 9:

Leserforum I Briefe, E-Mail, Hotlin

- Seite 10 und 11:

Leserforum I Briefe, E-Mail, Hotlin

- Seite 12 und 13:

ICIMME" Der Hype nervt! Entscheiden

- Seite 14 und 15:

Dr. Volker ZotaComputer-Geschichten

- Seite 16:

Prüfstand I Macßook Pro RetinaBen

- Seite 19:

Anzeige• •EUROPAISCHEEINHEITEur

- Seite 22 und 23:

Praxis I Windows-8.1-Updatetionsmö

- Seite 24 und 25:

aktuell I ProzessorenAndreas Stille

- Seite 26 und 27:

aktuell I iPad AirTomas RudlMehr al

- Seite 28 und 29:

aktuell I Smartphones und TabletsJ

- Seite 30 und 31:

aktuell I Atom-CPU für Serverparat

- Seite 32 und 33:

aktuell I Smartphones und TabletsAl

- Seite 34 und 35:

aktuell I HardwarePreiswerter Mini-

- Seite 36 und 37:

aktuell I Embedded64-Bit-Architektu

- Seite 38:

aktuell I NetzeTREnDnETPoE-Switch b

- Seite 41 und 42:

aktuell I PeripherieBiegsame Displa

- Seite 43 und 44:

aktuell I Technische AnwendungenInn

- Seite 45 und 46:

aktuell I AnwendungenHören statt l

- Seite 47 und 48:

...aktuell I LinuxSilverlight unter

- Seite 49 und 50:

Gitarrenspiel Rocksmith 2014201 2 t

- Seite 51 und 52:

DAS SPIELERLEBNIS DER NÄCHSTEN GEN

- Seite 53 und 54:

3:wz

- Seite 55 und 56:

aktuell I AppsBlackBerry Messenger

- Seite 57 und 58:

aktuell I PeripherieSamsung reicht

- Seite 59 und 60:

aktuell I SicherheitAufregung um Ü

- Seite 61 und 62:

Wir mptehlen Windows 8 Pro und Wind

- Seite 63 und 64:

kurz vorgestellt I DJ-Controller, U

- Seite 65 und 66:

kurz vorgestellt I Dateiaustausch,

- Seite 67:

kurz vorgestellt I Bildbearbeitung

- Seite 70 und 71:

Prüfstand I GrafikkartenMartin Fis

- Seite 72 und 73:

Prüfstand I Grafikkartenaufnahme u

- Seite 74 und 75:

Prüfstand I Firefox-HandyJo Bager,

- Seite 76 und 77:

Prüfstand I Software Defined Radio

- Seite 78 und 79:

..Report I Visual Studio 2013Hajo S

- Seite 80 und 81:

Report I Service & SupportGeorg Sch

- Seite 82 und 83:

Report I Service & SupportVorsicht

- Seite 84:

Report I NetzpolitikRichard Sietman

- Seite 87 und 88:

Report I NetzpolitikArtikel 24 den

- Seite 89 und 90:

thomas-krenn.comSichern Sie sich ei

- Seite 91 und 92:

Mild-erotische Abenteuer durfte man

- Seite 93 und 94:

Report I 30 Jahre ComputertechnikAp

- Seite 95 und 96:

Report I IT-Geschichtelichkeit, wie

- Seite 97:

SynologyOisk5tation 05214+ und 0541

- Seite 100:

Report 1 30 Jahre c'tGerald Himmele

- Seite 104 und 105:

Report I Ihr Wunsch-PC: Ka ufberatu

- Seite 106 und 107:

Report I Ihr Wunsch-PC: Ka ufberatu

- Seite 108 und 109:

Report I Ihr Wunsch-PC: Ka ufberatu

- Seite 110 und 111:

Report I Ihr Wunsch-PC: Ka ufberatu

- Seite 112 und 113:

Praxis I Ihr Wunsch-PC: Bauvorschl

- Seite 114 und 115:

Praxis I Ihr Wunsch-PC: Bauvorschl

- Seite 116 und 117:

Praxis I Ihr Wunsch-PC: Bauvorschl

- Seite 118 und 119:

Praxis I Ihr Wunsch-PC: Va riatione

- Seite 120 und 121:

Praxis I Ihr Wunsch-PC: Va riatione

- Seite 122:

Praxis I Ihr Wunsch-PC: Va riatione

- Seite 125 und 126:

und Bastelfreaks!Exklusive Sonderhe

- Seite 127 und 128:

Prüfstand I Riesen-Smartphoneser i

- Seite 129 und 130:

THE IT ARCHITECTSAls Tacllter der l

- Seite 131 und 132:

Prüfstand I Riesen-Smartphonespyra

- Seite 133 und 134:

Prüfsta nd I Riesen-Smartphonespyr

- Seite 135 und 136:

Prüfstand I Riesen-Smartphonesm3DM

- Seite 138 und 139:

Report I Tablet-AppsJörg WirtgenGr

- Seite 140 und 141:

Prüfstand I Fotos im WebAndre Kram

- Seite 142 und 143:

Prüfstand I Fotos im WebCloud-Foto

- Seite 144 und 145:

Prüfstand I Fotos im WebHausieren

- Seite 146 und 147:

Prüfstand I Fotos im Webper Schieb

- Seite 148 und 149:

Loslegen mit 3D-Druck3D-Druck-Tipps

- Seite 150 und 151:

Praxis I 3D-Druckdruckenden Objekts

- Seite 152 und 153:

Praxis I 3D-Druck- - :l. .. , .. .

- Seite 154 und 155:

fi':\hers Events.....heise Events K

- Seite 156 und 157:

Praxis I 3D-DruckPeter König, Andr

- Seite 158:

Praxis I 3D-DruckDrucker-Bausätzen

- Seite 162 und 163:

Report I 3D-DruckPeter KönigIndivi

- Seite 164 und 165:

Report I 3D-DruckSo unterschiedlich

- Seite 166 und 167:

USB viaNetzwerkReport I 3D-Drucksol

- Seite 168 und 169:

Arch Linux Vorrang vor Bequemlichke

- Seite 170 und 171: Report I Arch LinuxnXG 4 14.20 botu

- Seite 172 und 173: Know-how I MassenspeicherBoi Fedder

- Seite 174 und 175: Know-how I Massenspeichergriffe wie

- Seite 176 und 177: thomas-krenn.comKnow-how I Massensp

- Seite 178 und 179: Urs MansmannEs geht voranHoffnungss

- Seite 180 und 181: Report I Breitbandausbauund dem Mai

- Seite 182 und 183: Jöran Muuß-MerholzGeteiltes Wisse

- Seite 184: Report I Open Educational Resources

- Seite 187 und 188: Das bestePreis-Leistungs-verhältni

- Seite 189 und 190: Recht I Datenschutzliegt nunmehr im

- Seite 191 und 192: Praxis I HotlineSERVER ab und start

- Seite 193 und 194: Praxis I Hotlinezeigt die auf der W

- Seite 195 und 196: Praxis I FAQDie Kunst der Regelungt

- Seite 197 und 198: Praxis I DynDNS selbstgebaut• ;

- Seite 199 und 200: Praxis I DynDNS selbstgebautden SOA

- Seite 201 und 202: Praxis I Ka li LinuxTop 10 Secunty

- Seite 203 und 204: i:\ heise\!!: Events heise Events K

- Seite 205 und 206: Erst lesen,dann löten!c't Hacks -

- Seite 207 und 208: 1Praxis I Browser-EntwicklertoolsIm

- Seite 209 und 210: Praxis I Browser-Entwicklertoolsauf

- Seite 211 und 212: Praxis I Browser-EntwicklertoolsAPS

- Seite 213 und 214: Know-how I OpenGL ESsetRenderer(ren

- Seite 215 und 216: 2. Aujlage2013 · 312 Seiten · €

- Seite 218 und 219: Andreas StillerServerbastion voraus

- Seite 222 und 223: Praxis I Heim-ServerHajo SchulzDer

- Seite 224 und 225: Als Dankeschön fü r Sie legen wir

- Seite 226 und 227: Das ideale Bundle fürambitionierte

- Seite 229 und 230: - IQTHE ti4'.«17VUEqT -30 ./4H4'E

- Seite 231 und 232: PAESSLERthe network monitoring comp

- Seite 233 und 234: Wir gratulieren der c'therzlich zum

- Seite 235 und 236: Wi r gratulieren der c't zu m 3 0 G

- Seite 237 und 238: AMDOPTERONOpteron"' SOpteron'" MOpt

- Seite 239 und 240: l'f"\ Dualcore Cortex A9\,j;,l CPU

- Seite 241: HETZNER ROOT SERVER DELL, PowerEdge

- Seite 245 und 246: Onlinespeicher mit 100 GB1 ganzes J

- Seite 247 und 248: "So Jungs, heute seid Ihrmit Aufrä

- Seite 249 und 250: (metal(•1••• !J. . . . . .

- Seite 251 und 252: DER NEUE••LANGLAUFEHTRIATHLOR E

- Seite 253 und 254: Komplette WLAN Lösungen vom Hotspo

- Seite 256 und 257: Buchkritik I App-Entwicklung, IT-Be

- Seite 258 und 259: Spiele I Survivai-Scroller, Kombina

- Seite 260 und 261: Spiele I Adventures, Jump & Run:111

- Seite 262 und 263: Spiele I Rollenspiel, lndie- und Fr

- Seite 264 und 265: Kids' Bits I Geschicklichkeitsspiel

- Seite 267 und 268: öten Sie mich!"TDie junge Frau vor

- Seite 269 und 270: ICY BOXG Jetzt anmelden!Hyper-Vmit

- Seite 271 und 272:

Samsu ng 840 EVO 2,5" 250 GB Router

- Seite 273 und 274:

FRONTPLATTEN & GEHÄUSEKostengünst

- Seite 275 und 276:

l!>.=l6. MID-Die Konferenz der java

- Seite 277 und 278:

STELLENMARKTDie FRS-Reedereigruppe

- Seite 279 und 280:

SOFTWA RE STEUERT TEC HNIK.MIT SICH

- Seite 281 und 282:

Impressum I ServiceImpressumRedakti

- Seite 283 und 284:

Funktionen./ Telefonie, Voicemait,