MVME5100 Single Board Computer Programmer's Reference Guide

MVME5100 Single Board Computer Programmer's Reference Guide

MVME5100 Single Board Computer Programmer's Reference Guide

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

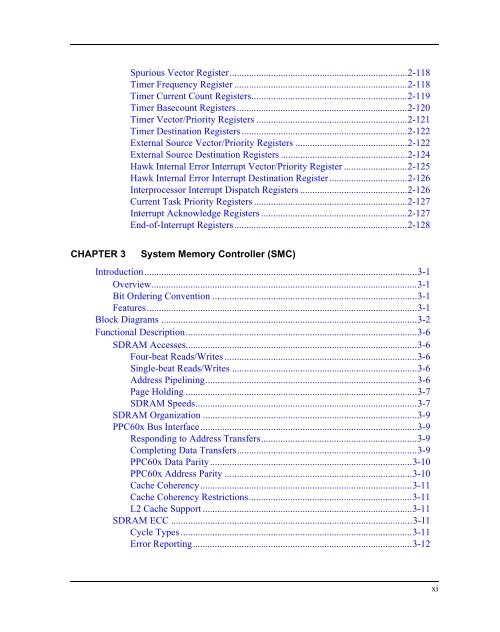

Spurious Vector Register.........................................................................2-118<br />

Timer Frequency Register .......................................................................2-118<br />

Timer Current Count Registers................................................................2-119<br />

Timer Basecount Registers......................................................................2-120<br />

Timer Vector/Priority Registers ..............................................................2-121<br />

Timer Destination Registers ....................................................................2-122<br />

External Source Vector/Priority Registers ..............................................2-122<br />

External Source Destination Registers ....................................................2-124<br />

Hawk Internal Error Interrupt Vector/Priority Register ..........................2-125<br />

Hawk Internal Error Interrupt Destination Register................................2-126<br />

Interprocessor Interrupt Dispatch Registers ............................................2-126<br />

Current Task Priority Registers ...............................................................2-127<br />

Interrupt Acknowledge Registers ............................................................2-127<br />

End-of-Interrupt Registers.......................................................................2-128<br />

CHAPTER 3 System Memory Controller (SMC)<br />

Introduction................................................................................................................3-1<br />

Overview.............................................................................................................3-1<br />

Bit Ordering Convention ....................................................................................3-1<br />

Features...............................................................................................................3-1<br />

Block Diagrams .........................................................................................................3-2<br />

Functional Description...............................................................................................3-6<br />

SDRAM Accesses...............................................................................................3-6<br />

Four-beat Reads/Writes ...............................................................................3-6<br />

<strong>Single</strong>-beat Reads/Writes ............................................................................3-6<br />

Address Pipelining.......................................................................................3-6<br />

Page Holding ...............................................................................................3-7<br />

SDRAM Speeds...........................................................................................3-7<br />

SDRAM Organization ........................................................................................3-9<br />

PPC60x Bus Interface.........................................................................................3-9<br />

Responding to Address Transfers................................................................3-9<br />

Completing Data Transfers..........................................................................3-9<br />

PPC60x Data Parity...................................................................................3-10<br />

PPC60x Address Parity .............................................................................3-10<br />

Cache Coherency.......................................................................................3-11<br />

Cache Coherency Restrictions...................................................................3-11<br />

L2 Cache Support ......................................................................................3-11<br />

SDRAM ECC ...................................................................................................3-11<br />

Cycle Types ...............................................................................................3-11<br />

Error Reporting..........................................................................................3-12<br />

xi