MVME5100 Single Board Computer Programmer's Reference Guide

MVME5100 Single Board Computer Programmer's Reference Guide

MVME5100 Single Board Computer Programmer's Reference Guide

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

3<br />

System Memory Controller (SMC)<br />

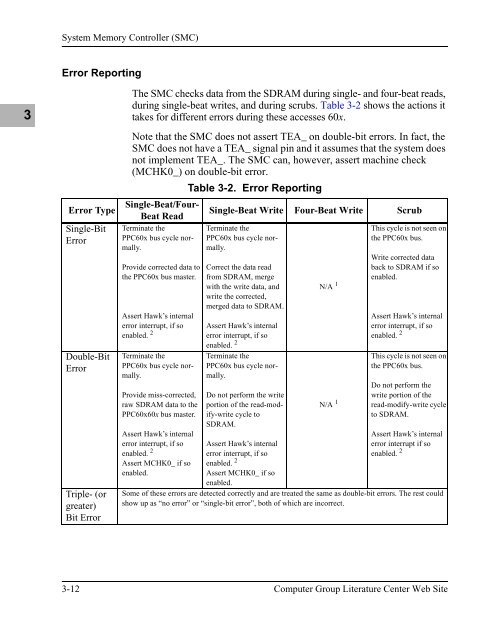

Error Reporting<br />

The SMC checks data from the SDRAM during single- and four-beat reads,<br />

during single-beat writes, and during scrubs. Table 3-2 shows the actions it<br />

takes for different errors during these accesses 60x.<br />

Note that the SMC does not assert TEA_ on double-bit errors. In fact, the<br />

SMC does not have a TEA_ signal pin and it assumes that the system does<br />

not implement TEA_. The SMC can, however, assert machine check<br />

(MCHK0_) on double-bit error.<br />

Table 3-2. Error Reporting<br />

Error Type <strong>Single</strong>-Beat/Four-<br />

<strong>Single</strong>-Beat Write Four-Beat Write Scrub<br />

Beat Read<br />

<strong>Single</strong>-Bit<br />

Error<br />

Double-Bit<br />

Error<br />

Triple- (or<br />

greater)<br />

Bit Error<br />

Terminate the<br />

PPC60x bus cycle normally.<br />

Provide corrected data to<br />

the PPC60x bus master.<br />

Assert Hawk’s internal<br />

error interrupt, if so<br />

enabled. 2<br />

Terminate the<br />

PPC60x bus cycle normally.<br />

Provide miss-corrected,<br />

raw SDRAM data to the<br />

PPC60x60x bus master.<br />

Assert Hawk’s internal<br />

error interrupt, if so<br />

enabled. 2<br />

Assert MCHK0_ if so<br />

enabled.<br />

Terminate the<br />

PPC60x bus cycle normally.<br />

Correct the data read<br />

from SDRAM, merge<br />

with the write data, and<br />

write the corrected,<br />

merged data to SDRAM.<br />

Assert Hawk’s internal<br />

error interrupt, if so<br />

enabled. 2<br />

Terminate the<br />

PPC60x bus cycle normally.<br />

Do not perform the write<br />

portion of the read-modify-write<br />

cycle to<br />

SDRAM.<br />

Assert Hawk’s internal<br />

error interrupt, if so<br />

enabled. 2<br />

Assert MCHK0_ if so<br />

enabled.<br />

3-12 <strong>Computer</strong> Group Literature Center Web Site<br />

N/A 1<br />

N/A 1<br />

This cycle is not seen on<br />

the PPC60x bus.<br />

Write corrected data<br />

back to SDRAM if so<br />

enabled.<br />

Assert Hawk’s internal<br />

error interrupt, if so<br />

enabled. 2<br />

This cycle is not seen on<br />

the PPC60x bus.<br />

Do not perform the<br />

write portion of the<br />

read-modify-write cycle<br />

to SDRAM.<br />

Assert Hawk’s internal<br />

error interrupt if so<br />

enabled. 2<br />

Some of these errors are detected correctly and are treated the same as double-bit errors. The rest could<br />

show up as “no error” or “single-bit error”, both of which are incorrect.