MVME5100 Single Board Computer Programmer's Reference Guide

MVME5100 Single Board Computer Programmer's Reference Guide

MVME5100 Single Board Computer Programmer's Reference Guide

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

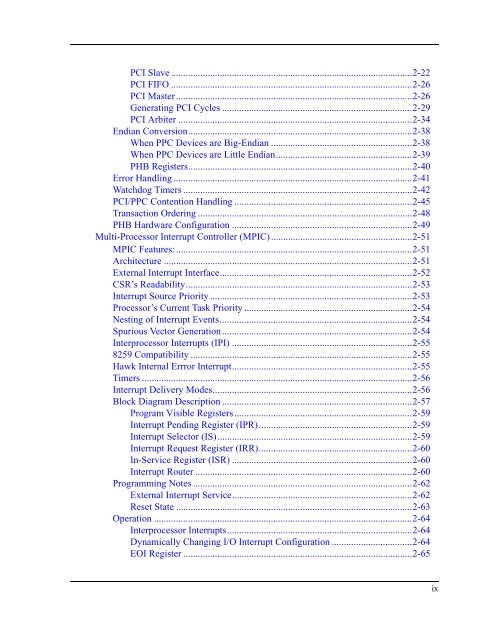

PCI Slave ...................................................................................................2-22<br />

PCI FIFO ...................................................................................................2-26<br />

PCI Master.................................................................................................2-26<br />

Generating PCI Cycles ..............................................................................2-29<br />

PCI Arbiter ................................................................................................2-34<br />

Endian Conversion............................................................................................2-38<br />

When PPC Devices are Big-Endian ..........................................................2-38<br />

When PPC Devices are Little Endian........................................................2-39<br />

PHB Registers............................................................................................2-40<br />

Error Handling ..................................................................................................2-41<br />

Watchdog Timers ..............................................................................................2-42<br />

PCI/PPC Contention Handling .........................................................................2-45<br />

Transaction Ordering ........................................................................................2-48<br />

PHB Hardware Configuration ..........................................................................2-49<br />

Multi-Processor Interrupt Controller (MPIC)..........................................................2-51<br />

MPIC Features: .................................................................................................2-51<br />

Architecture ......................................................................................................2-51<br />

External Interrupt Interface...............................................................................2-52<br />

CSR’s Readability.............................................................................................2-53<br />

Interrupt Source Priority ...................................................................................2-53<br />

Processor’s Current Task Priority .....................................................................2-54<br />

Nesting of Interrupt Events...............................................................................2-54<br />

Spurious Vector Generation..............................................................................2-54<br />

Interprocessor Interrupts (IPI) ..........................................................................2-55<br />

8259 Compatibility ...........................................................................................2-55<br />

Hawk Internal Errror Interrupt..........................................................................2-55<br />

Timers ...............................................................................................................2-56<br />

Interrupt Delivery Modes..................................................................................2-56<br />

Block Diagram Description ..............................................................................2-57<br />

Program Visible Registers.........................................................................2-59<br />

Interrupt Pending Register (IPR)...............................................................2-59<br />

Interrupt Selector (IS)................................................................................2-59<br />

Interrupt Request Register (IRR)...............................................................2-60<br />

In-Service Register (ISR) ..........................................................................2-60<br />

Interrupt Router .........................................................................................2-60<br />

Programming Notes ..........................................................................................2-62<br />

External Interrupt Service..........................................................................2-62<br />

Reset State .................................................................................................2-63<br />

Operation ..........................................................................................................2-64<br />

Interprocessor Interrupts............................................................................2-64<br />

Dynamically Changing I/O Interrupt Configuration .................................2-64<br />

EOI Register ..............................................................................................2-65<br />

ix