characterization, modeling, and design of esd protection circuits

characterization, modeling, and design of esd protection circuits

characterization, modeling, and design of esd protection circuits

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

144 Chapter 5. Design <strong>and</strong> Optimization <strong>of</strong> ESD Protection Transistor Layout<br />

certain charging voltage, VHBM , the 1500Ω series resistor <strong>of</strong> the circuit is usually much<br />

larger than the impedance <strong>of</strong> the device under test, so we can think <strong>of</strong> both TLP <strong>and</strong> HBM<br />

testers as current sources, with the peak HBM current equal to VHBM /1500Ω. For the<br />

Advanced Micro Devices (AMD) 0.35µm technology studied in this chapter, we know<br />

from failure analysis that HBM <strong>and</strong> TLP failures are thermal rather than dielectric in<br />

nature. An identical failure mechanism leads us to believe that there may be some TLP<br />

pulse width for which the withst<strong>and</strong> current, ITLP,ws , <strong>of</strong> any structure is equal to the peak<br />

current <strong>of</strong> an HBM pulse at the withst<strong>and</strong> level <strong>of</strong> that structure. Note that from this point<br />

on the TLP failure current, It2 or Ifail , is assumed to be only infinitesimally larger than the<br />

withst<strong>and</strong> current (the maximum TLP current a structure can withst<strong>and</strong> without incurring<br />

damage), so all terms are used interchangeably.<br />

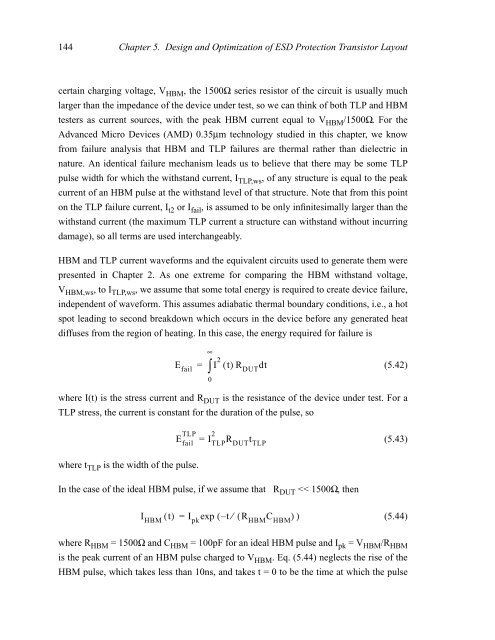

HBM <strong>and</strong> TLP current waveforms <strong>and</strong> the equivalent <strong>circuits</strong> used to generate them were<br />

presented in Chapter 2. As one extreme for comparing the HBM withst<strong>and</strong> voltage,<br />

VHBM,ws , to ITLP,ws , we assume that some total energy is required to create device failure,<br />

independent <strong>of</strong> waveform. This assumes adiabatic thermal boundary conditions, i.e., a hot<br />

spot leading to second breakdown which occurs in the device before any generated heat<br />

diffuses from the region <strong>of</strong> heating. In this case, the energy required for failure is<br />

(5.42)<br />

where I(t) is the stress current <strong>and</strong> RDUT is the resistance <strong>of</strong> the device under test. For a<br />

TLP stress, the current is constant for the duration <strong>of</strong> the pulse, so<br />

where t TLP is the width <strong>of</strong> the pulse.<br />

∞<br />

∫<br />

Efail I 2 = ()R t DUTdt TLP<br />

Efail 0<br />

2<br />

= ITLPRDUTtTLP In the case <strong>of</strong> the ideal HBM pulse, if we assume that R DUT