Manual - 8500A Series Peak Power Meter - Giga-tronics

Manual - 8500A Series Peak Power Meter - Giga-tronics

Manual - 8500A Series Peak Power Meter - Giga-tronics

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

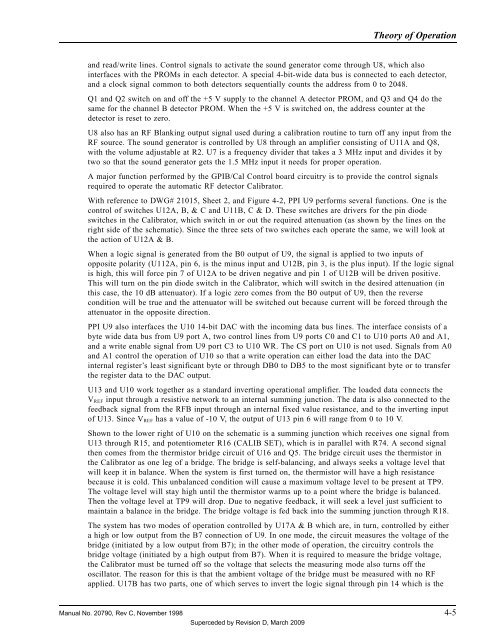

Theory of Operation<br />

and read/write lines. Control signals to activate the sound generator come through U8, which also<br />

interfaces with the PROMs in each detector. A special 4-bit-wide data bus is connected to each detector,<br />

and a clock signal common to both detectors sequentially counts the address from 0 to 2048.<br />

Q1 and Q2 switch on and off the +5 V supply to the channel A detector PROM, and Q3 and Q4 do the<br />

same for the channel B detector PROM. When the +5 V is switched on, the address counter at the<br />

detector is reset to zero.<br />

U8 also has an RF Blanking output signal used during a calibration routine to turn off any input from the<br />

RF source. The sound generator is controlled by U8 through an amplifier consisting of U11A and Q8,<br />

with the volume adjustable at R2. U7 is a frequency divider that takes a 3 MHz input and divides it by<br />

two so that the sound generator gets the 1.5 MHz input it needs for proper operation.<br />

A major function performed by the GPIB/Cal Control board circuitry is to provide the control signals<br />

required to operate the automatic RF detector Calibrator.<br />

With reference to DWG# 21015, Sheet 2, and Figure 4-2, PPI U9 performs several functions. One is the<br />

control of switches U12A, B, & C and U11B, C & D. These switches are drivers for the pin diode<br />

switches in the Calibrator, which switch in or out the required attenuation (as shown by the lines on the<br />

right side of the schematic). Since the three sets of two switches each operate the same, we will look at<br />

the action of U12A & B.<br />

When a logic signal is generated from the B0 output of U9, the signal is applied to two inputs of<br />

opposite polarity (U112A, pin 6, is the minus input and U12B, pin 3, is the plus input). If the logic signal<br />

is high, this will force pin 7 of U12A to be driven negative and pin 1 of U12B will be driven positive.<br />

This will turn on the pin diode switch in the Calibrator, which will switch in the desired attenuation (in<br />

this case, the 10 dB attenuator). If a logic zero comes from the B0 output of U9, then the reverse<br />

condition will be true and the attenuator will be switched out because current will be forced through the<br />

attenuator in the opposite direction.<br />

PPI U9 also interfaces the U10 14-bit DAC with the incoming data bus lines. The interface consists of a<br />

byte wide data bus from U9 port A, two control lines from U9 ports C0 and C1 to U10 ports A0 and A1,<br />

and a write enable signal from U9 port C3 to U10 WR. The CS port on U10 is not used. Signals from A0<br />

and A1 control the operation of U10 so that a write operation can either load the data into the DAC<br />

internal register’s least significant byte or through DB0 to DB5 to the most significant byte or to transfer<br />

the register data to the DAC output.<br />

U13 and U10 work together as a standard inverting operational amplifier. The loaded data connects the<br />

V REF input through a resistive network to an internal summing junction. The data is also connected to the<br />

feedback signal from the RFB input through an internal fixed value resistance, and to the inverting input<br />

of U13. Since V REF has a value of -10 V, the output of U13 pin 6 will range from 0 to 10 V.<br />

Shown to the lower right of U10 on the schematic is a summing junction which receives one signal from<br />

U13 through R15, and potentiometer R16 (CALIB SET), which is in parallel with R74. A second signal<br />

then comes from the thermistor bridge circuit of U16 and Q5. The bridge circuit uses the thermistor in<br />

the Calibrator as one leg of a bridge. The bridge is self-balancing, and always seeks a voltage level that<br />

will keep it in balance. When the system is first turned on, the thermistor will have a high resistance<br />

because it is cold. This unbalanced condition will cause a maximum voltage level to be present at TP9.<br />

The voltage level will stay high until the thermistor warms up to a point where the bridge is balanced.<br />

Then the voltage level at TP9 will drop. Due to negative feedback, it will seek a level just sufficient to<br />

maintain a balance in the bridge. The bridge voltage is fed back into the summing junction through R18.<br />

The system has two modes of operation controlled by U17A & B which are, in turn, controlled by either<br />

a high or low output from the B7 connection of U9. In one mode, the circuit measures the voltage of the<br />

bridge (initiated by a low output from B7); in the other mode of operation, the circuitry controls the<br />

bridge voltage (initiated by a high output from B7). When it is required to measure the bridge voltage,<br />

the Calibrator must be turned off so the voltage that selects the measuring mode also turns off the<br />

oscillator. The reason for this is that the ambient voltage of the bridge must be measured with no RF<br />

applied. U17B has two parts, one of which serves to invert the logic signal through pin 14 which is the<br />

<strong>Manual</strong> No. 20790, Rev C, November 1998 4-5<br />

Superceded by Revision D, March 2009