Xilinx Constraints Guide

Xilinx Constraints Guide

Xilinx Constraints Guide

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 4: <strong>Xilinx</strong> <strong>Constraints</strong><br />

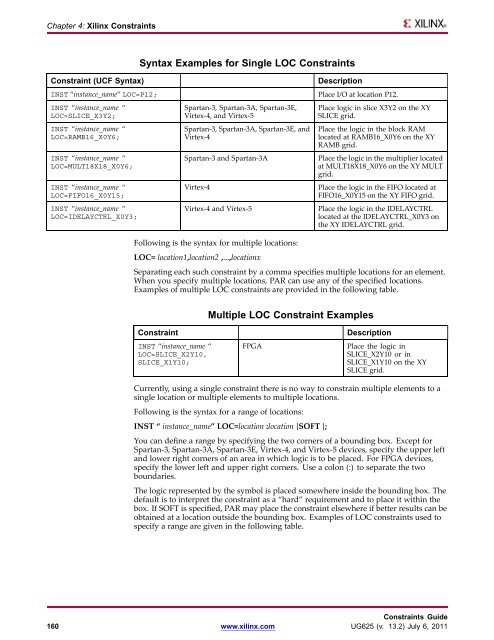

Syntax Examples for Single LOC <strong>Constraints</strong><br />

Constraint (UCF Syntax) Description<br />

INST “instance_name” LOC=P12; Place I/O at location P12.<br />

INST “instance_name “<br />

LOC=SLICE_X3Y2;<br />

INST “instance_name “<br />

LOC=RAMB16_X0Y6;<br />

INST “instance_name “<br />

LOC=MULT18X18_X0Y6;<br />

INST “instance_name “<br />

LOC=FIFO16_X0Y15;<br />

INST “instance_name “<br />

LOC=IDELAYCTRL_X0Y3;<br />

Spartan-3, Spartan-3A, Spartan-3E,<br />

Virtex-4, and Virtex-5<br />

Spartan-3, Spartan-3A, Spartan-3E, and<br />

Virtex-4<br />

Place logic in slice X3Y2 on the XY<br />

SLICE grid.<br />

Place the logic in the block RAM<br />

located at RAMB16_X0Y6 on the XY<br />

RAMB grid.<br />

Spartan-3 and Spartan-3A Place the logic in the multiplier located<br />

at MULT18X18_X0Y6 on the XY MULT<br />

grid.<br />

Virtex-4 Place the logic in the FIFO located at<br />

FIFO16_X0Y15 on the XY FIFO grid.<br />

Virtex-4 and Virtex-5 Place the logic in the IDELAYCTRL<br />

located at the IDELAYCTRL_X0Y3 on<br />

the XY IDELAYCTRL grid.<br />

Following is the syntax for multiple locations:<br />

LOC= location1,location2 ,...,locationx<br />

Separating each such constraint by a comma specifies multiple locations for an element.<br />

When you specify multiple locations, PAR can use any of the specified locations.<br />

Examples of multiple LOC constraints are provided in the following table.<br />

Multiple LOC Constraint Examples<br />

Constraint Description<br />

INST “instance_name “<br />

LOC=SLICE_X2Y10,<br />

SLICE_X1Y10;<br />

FPGA Place the logic in<br />

SLICE_X2Y10 or in<br />

SLICE_X1Y10 on the XY<br />

SLICE grid.<br />

Currently, using a single constraint there is no way to constrain multiple elements to a<br />

single location or multiple elements to multiple locations.<br />

Following is the syntax for a range of locations:<br />

INST “ instance_name” LOC=location :location {SOFT };<br />

You can define a range by specifying the two corners of a bounding box. Except for<br />

Spartan-3, Spartan-3A, Spartan-3E, Virtex-4, and Virtex-5 devices, specify the upper left<br />

and lower right corners of an area in which logic is to be placed. For FPGA devices,<br />

specify the lower left and upper right corners. Use a colon (:) to separate the two<br />

boundaries.<br />

The logic represented by the symbol is placed somewhere inside the bounding box. The<br />

default is to interpret the constraint as a “hard” requirement and to place it within the<br />

box. If SOFT is specified, PAR may place the constraint elsewhere if better results can be<br />

obtained at a location outside the bounding box. Examples of LOC constraints used to<br />

specify a range are given in the following table.<br />

<strong>Constraints</strong> <strong>Guide</strong><br />

160 www.xilinx.com UG625 (v. 13.2) July 6, 2011