Xilinx Constraints Guide

Xilinx Constraints Guide

Xilinx Constraints Guide

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 2: Entry Strategies for <strong>Xilinx</strong> <strong>Constraints</strong><br />

FPGA Editor<br />

You can add or delete certain constraints in the Physical <strong>Constraints</strong> File (PCF) using<br />

FPGA Editor. FPGA Editor supports net, site, and component constraints as property<br />

fields in the individual nets and components. Properties are set with the Setattr<br />

command, and are read with the Getattr command.<br />

All Boolean constraints, including BLOCK, Locate (LOCATE), LOCK, Offset In (OFFSET<br />

IN), Offset Out (OFFSET OUT), and Prohibit (PROHIBIT), have values of On or Off.<br />

Offset direction has a value of either In or Out. Offset order has a value of either Before<br />

or After. All other constraints have a numeric value. They can also be set to Off in<br />

order to delete the constraint. All values are case-insensitive (for example, On and on<br />

are both accepted).<br />

When you create a constraint in the FPGA Editor, the constraint is written to the PCF file<br />

whenever you save your design. When you use the FPGA Editor to delete a constraint,<br />

and then save your design file, the line on which the constraint appears in the PCF<br />

file remains in the file but is automatically commented out. Some of the constraints<br />

supported in the FPGA Editor are listed in the following table.<br />

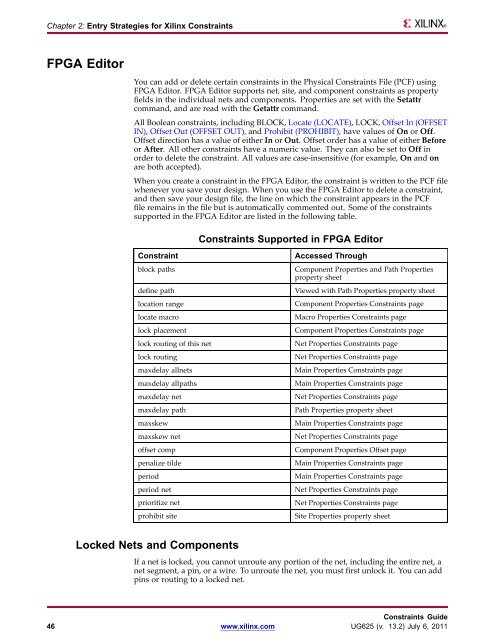

<strong>Constraints</strong> Supported in FPGA Editor<br />

Constraint Accessed Through<br />

block paths Component Properties and Path Properties<br />

property sheet<br />

define path Viewed with Path Properties property sheet<br />

location range Component Properties <strong>Constraints</strong> page<br />

locate macro Macro Properties <strong>Constraints</strong> page<br />

lock placement Component Properties <strong>Constraints</strong> page<br />

lock routing of this net Net Properties <strong>Constraints</strong> page<br />

lock routing Net Properties <strong>Constraints</strong> page<br />

maxdelay allnets Main Properties <strong>Constraints</strong> page<br />

maxdelay allpaths Main Properties <strong>Constraints</strong> page<br />

maxdelay net Net Properties <strong>Constraints</strong> page<br />

maxdelay path Path Properties property sheet<br />

maxskew Main Properties <strong>Constraints</strong> page<br />

maxskew net Net Properties <strong>Constraints</strong> page<br />

offset comp Component Properties Offset page<br />

penalize tilde Main Properties <strong>Constraints</strong> page<br />

period Main Properties <strong>Constraints</strong> page<br />

period net Net Properties <strong>Constraints</strong> page<br />

prioritize net Net Properties <strong>Constraints</strong> page<br />

prohibit site Site Properties property sheet<br />

Locked Nets and Components<br />

If a net is locked, you cannot unroute any portion of the net, including the entire net, a<br />

net segment, a pin, or a wire. To unroute the net, you must first unlock it. You can add<br />

pins or routing to a locked net.<br />

<strong>Constraints</strong> <strong>Guide</strong><br />

46 www.xilinx.com UG625 (v. 13.2) July 6, 2011