Xilinx Constraints Guide

Xilinx Constraints Guide

Xilinx Constraints Guide

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 4: <strong>Xilinx</strong> <strong>Constraints</strong><br />

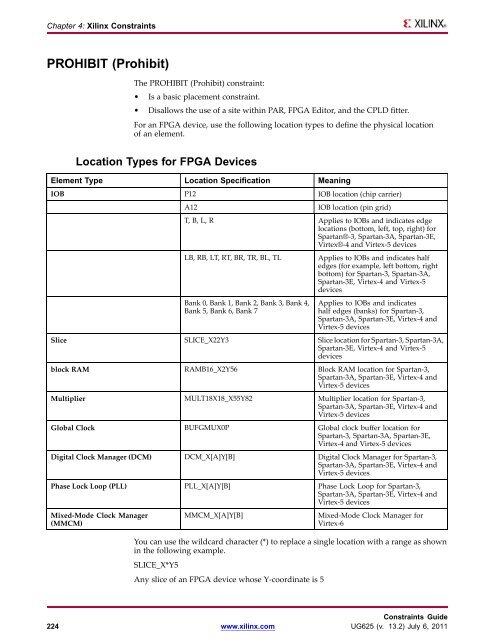

PROHIBIT (Prohibit)<br />

The PROHIBIT (Prohibit) constraint:<br />

• Is a basic placement constraint.<br />

• Disallows the use of a site within PAR, FPGA Editor, and the CPLD fitter.<br />

For an FPGA device, use the following location types to define the physical location<br />

of an element.<br />

Location Types for FPGA Devices<br />

Element Type Location Specification Meaning<br />

IOB P12 IOB location (chip carrier)<br />

A12 IOB location (pin grid)<br />

T, B, L, R Applies to IOBs and indicates edge<br />

locations (bottom, left, top, right) for<br />

Spartan®-3, Spartan-3A, Spartan-3E,<br />

Virtex®-4 and Virtex-5 devices<br />

LB, RB, LT, RT, BR, TR, BL, TL Applies to IOBs and indicates half<br />

edges (for example, left bottom, right<br />

bottom) for Spartan-3, Spartan-3A,<br />

Spartan-3E, Virtex-4 and Virtex-5<br />

devices<br />

Bank 0, Bank 1, Bank 2, Bank 3, Bank 4,<br />

Bank 5, Bank 6, Bank 7<br />

Applies to IOBs and indicates<br />

half edges (banks) for Spartan-3,<br />

Spartan-3A, Spartan-3E, Virtex-4 and<br />

Virtex-5 devices<br />

Slice SLICE_X22Y3 Slice location for Spartan-3, Spartan-3A,<br />

Spartan-3E, Virtex-4 and Virtex-5<br />

devices<br />

block RAM RAMB16_X2Y56 Block RAM location for Spartan-3,<br />

Spartan-3A, Spartan-3E, Virtex-4 and<br />

Virtex-5 devices<br />

Multiplier MULT18X18_X55Y82 Multiplier location for Spartan-3,<br />

Spartan-3A, Spartan-3E, Virtex-4 and<br />

Virtex-5 devices<br />

Global Clock BUFGMUX0P Global clock buffer location for<br />

Spartan-3, Spartan-3A, Spartan-3E,<br />

Virtex-4 and Virtex-5 devices<br />

Digital Clock Manager (DCM) DCM_X[A]Y[B] Digital Clock Manager for Spartan-3,<br />

Spartan-3A, Spartan-3E, Virtex-4 and<br />

Virtex-5 devices<br />

Phase Lock Loop (PLL) PLL_X[A]Y[B] Phase Lock Loop for Spartan-3,<br />

Spartan-3A, Spartan-3E, Virtex-4 and<br />

Virtex-5 devices<br />

Mixed-Mode Clock Manager<br />

(MMCM)<br />

MMCM_X[A]Y[B] Mixed-Mode Clock Manager for<br />

Virtex-6<br />

You can use the wildcard character (*) to replace a single location with a range as shown<br />

in the following example.<br />

SLICE_X*Y5<br />

Any slice of an FPGA device whose Y-coordinate is 5<br />

<strong>Constraints</strong> <strong>Guide</strong><br />

224 www.xilinx.com UG625 (v. 13.2) July 6, 2011