Chapter 10 Memory Subsystem.pdf

Chapter 10 Memory Subsystem.pdf

Chapter 10 Memory Subsystem.pdf

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

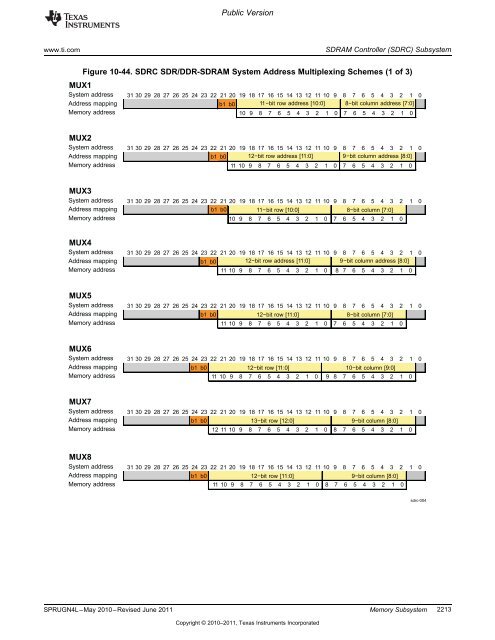

MUX1<br />

System address 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0<br />

Address mapping b1 b0 11−bit row address [<strong>10</strong>:0] 8−bit column address [7:0]<br />

<strong>Memory</strong> address <strong>10</strong> 9 8 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0<br />

MUX2<br />

System address<br />

Address mapping<br />

<strong>Memory</strong> address<br />

MUX3<br />

System address<br />

Address mapping<br />

<strong>Memory</strong> address<br />

MUX4<br />

System address<br />

Address mapping<br />

<strong>Memory</strong> address<br />

MUX5<br />

System address<br />

Address mapping<br />

<strong>Memory</strong> address<br />

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0<br />

b1 b0 12−bit<br />

row address [11:0] 9−bit<br />

column address [8:0]<br />

11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0<br />

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0<br />

b1 b0 11−bit<br />

row [<strong>10</strong>:0]<br />

8−bit<br />

column [7:0]<br />

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0<br />

b1 b0 12−bit<br />

row address [11:0] 9−bit<br />

column address [8:0]<br />

11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0 8 7 6 5 4 3 2 1 0<br />

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0<br />

b1 b0<br />

<strong>10</strong> 9 8 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0<br />

11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0<br />

MUX6<br />

System address 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0<br />

Address mapping b1 b0<br />

12−bit row [11:0]<br />

<strong>10</strong>−bit column [9:0]<br />

<strong>Memory</strong> address 11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0<br />

MUX7<br />

System address<br />

Address mapping<br />

<strong>Memory</strong> address<br />

MUX8<br />

System address<br />

Address mapping<br />

<strong>Memory</strong> address<br />

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0<br />

b1 b0<br />

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0<br />

b1 b0<br />

Public Version<br />

www.ti.com SDRAM Controller (SDRC) <strong>Subsystem</strong><br />

Figure <strong>10</strong>-44. SDRC SDR/DDR-SDRAM System Address Multiplexing Schemes (1 of 3)<br />

12−bit<br />

row [11:0]<br />

13−bit<br />

row [12:0]<br />

8−bit<br />

column [7:0]<br />

9−bit<br />

column [8:0]<br />

12 11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0 8 7 6 5 4 3 2 1 0<br />

12−bit<br />

row [11:0]<br />

9−bit<br />

column [8:0]<br />

11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0 8 7 6 5 4 3 2 1 0<br />

SPRUGN4L–May 20<strong>10</strong>–Revised June 2011 <strong>Memory</strong> <strong>Subsystem</strong><br />

Copyright © 20<strong>10</strong>–2011, Texas Instruments Incorporated<br />

sdrc-004<br />

2213