- Page 1 and 2: This chapter describes the memory s

- Page 3 and 4: Device GPMC External device/ memory

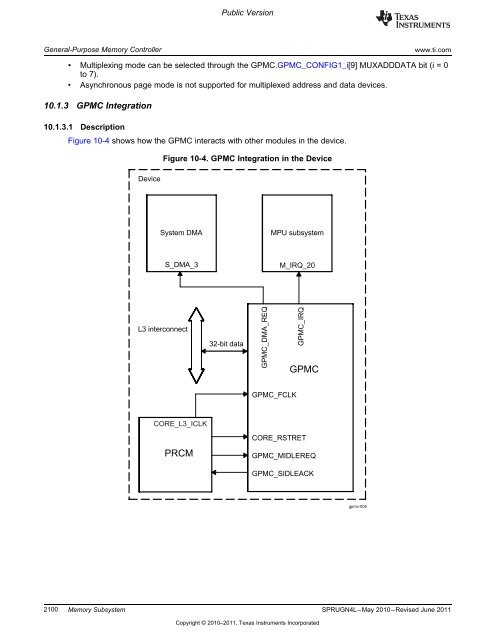

- Page 5: Public Version www.ti.com General-P

- Page 9 and 10: Public Version www.ti.com General-P

- Page 11 and 12: Public Version www.ti.com General-P

- Page 13 and 14: 1 GBytes 512 MBytes 256 MBytes 128

- Page 15 and 16: Public Version www.ti.com General-P

- Page 17 and 18: GPMC_FCLK GPMC_CLK gpmc_a[11:1] (co

- Page 19 and 20: Public Version www.ti.com General-P

- Page 21 and 22: Public Version www.ti.com General-P

- Page 23 and 24: GPMC_FCLK GPMC_CLK gpmc_a[11:1] (co

- Page 25 and 26: GPMC_FCLK GPMC_CLK gpmc_a[11:1] gpm

- Page 27 and 28: Public Version www.ti.com General-P

- Page 29 and 30: GPMC_FCLK GPMC_CLK gpmc_a[11:1] (co

- Page 31 and 32: Public Version www.ti.com General-P

- Page 33 and 34: GPMC_FCLK GPMC_CLK gpmc_a[11:1] (co

- Page 35 and 36: Public Version www.ti.com General-P

- Page 37 and 38: GPMC_FCLK GPMC_CLK gpmc_a[11:1] (co

- Page 39 and 40: GPMC_FCLK GPMC_CLK gpmc_a[11:1] (co

- Page 41 and 42: GPMC_FCLK GPMC_CLK gpmc_a[11:1] (co

- Page 43 and 44: GPMC_FCLK GPMC_CLK gpmc_a[11:1] gpm

- Page 45 and 46: Public Version www.ti.com General-P

- Page 47 and 48: nCS nBE0/CLE nWE nADV/ALE CSONTIME=

- Page 49 and 50: nCS nBE0/CLE nWE Public Version www

- Page 51 and 52: Public Version www.ti.com General-P

- Page 53 and 54: Row 0 Row 1 Row 2 Row 3 Row 252 Row

- Page 55 and 56: 512 Bytes input Row 0 Row 1 Row 2 R

- Page 57 and 58:

Public Version www.ti.com General-P

- Page 59 and 60:

Public Version www.ti.com General-P

- Page 61 and 62:

M0 Manual mode Rd/Wr/ SW Mode Size0

- Page 63 and 64:

Public Version www.ti.com General-P

- Page 65 and 66:

M1 M2 M3 M4 Per-sector spares Spare

- Page 67 and 68:

M9 Per-sector spares, separate ECC

- Page 69 and 70:

Public Version www.ti.com General-P

- Page 71 and 72:

Public Version www.ti.com General-P

- Page 73 and 74:

GPMC_FCLK nCS nBE0/CLE nOE/nRE nADV

- Page 75 and 76:

Device GPMC module A [27:17] A [16:

- Page 77 and 78:

FCLK CLK nADV nCS nOE A/D bus ClkAc

- Page 79 and 80:

FCLK nCS nADV nWE A/D bus AdvWrOffT

- Page 81 and 82:

Public Version www.ti.com General-P

- Page 83 and 84:

Public Version www.ti.com General-P

- Page 85 and 86:

Public Version www.ti.com General-P

- Page 87 and 88:

Public Version www.ti.com General-P

- Page 89 and 90:

Public Version www.ti.com General-P

- Page 91 and 92:

Public Version www.ti.com General-P

- Page 93 and 94:

Public Version www.ti.com General-P

- Page 95 and 96:

Public Version www.ti.com General-P

- Page 97 and 98:

Public Version www.ti.com General-P

- Page 99 and 100:

Public Version www.ti.com General-P

- Page 101 and 102:

Public Version www.ti.com General-P

- Page 103 and 104:

Public Version www.ti.com General-P

- Page 105 and 106:

Public Version www.ti.com General-P

- Page 107 and 108:

Public Version www.ti.com General-P

- Page 109 and 110:

Public Version www.ti.com General-P

- Page 111 and 112:

Public Version www.ti.com SDRAM Con

- Page 113 and 114:

Public Version www.ti.com SDRAM Con

- Page 115 and 116:

Device SDRAM controller subsystem R

- Page 117 and 118:

Public Version www.ti.com SDRAM Con

- Page 119 and 120:

MUX1 System address 31 30 29 28 27

- Page 121 and 122:

MUX23 System address Address mappin

- Page 123 and 124:

Public Version www.ti.com SDRAM Con

- Page 125 and 126:

Configuration register file Rotatio

- Page 127 and 128:

Public Version www.ti.com SDRAM Con

- Page 129 and 130:

Public Version www.ti.com SDRAM Con

- Page 131 and 132:

Level 0 Region 0 Public Version www

- Page 133 and 134:

Public Version www.ti.com SDRAM Con

- Page 135 and 136:

OCP slave interface OCP slave port

- Page 137 and 138:

Public Version www.ti.com SDRAM Con

- Page 139 and 140:

BANKALLOCATION = 0b00 BANKALLOCATIO

- Page 141 and 142:

Public Version www.ti.com SDRAM Con

- Page 143 and 144:

Endianism CSnMUXCFG field SDRC.SDRC

- Page 145 and 146:

Public Version www.ti.com SDRAM Con

- Page 147 and 148:

Public Version www.ti.com SDRAM Con

- Page 149 and 150:

CLK CMD WRITE DQ DQS CLK CMD DQ DQS

- Page 151 and 152:

CLK_IN SIGNAL_IN MODEMAXDELAY Initi

- Page 153 and 154:

Public Version www.ti.com SDRAM Con

- Page 155 and 156:

Public Version www.ti.com SDRAM Con

- Page 157 and 158:

Public Version www.ti.com SDRAM Con

- Page 159 and 160:

Public Version www.ti.com SDRAM Con

- Page 161 and 162:

Public Version www.ti.com SDRAM Con

- Page 163 and 164:

Public Version www.ti.com SDRAM Con

- Page 165 and 166:

Public Version www.ti.com SDRAM Con

- Page 167 and 168:

8 bits 32 bits Y0 U Y1 V P0 P1 16 b

- Page 169 and 170:

Start configuration of VRFB context

- Page 171 and 172:

Initiator: Camera subsystem SDRC Su

- Page 173 and 174:

Public Version www.ti.com SDRAM Con

- Page 175 and 176:

Request for transaction on class 1

- Page 177 and 178:

Class 1 and class 2 request for tra

- Page 179 and 180:

No A Class 0 empty? Yes Class 1 emp

- Page 181 and 182:

Status: There are n pending request

- Page 183 and 184:

4 GB 0x0000 0000 0x6C00 0000 0x6CFF

- Page 185 and 186:

Public Version www.ti.com SDRAM Con

- Page 187 and 188:

Public Version www.ti.com SDRAM Con

- Page 189 and 190:

Public Version www.ti.com SDRAM Con

- Page 191 and 192:

Public Version www.ti.com SDRAM Con

- Page 193 and 194:

Public Version www.ti.com SDRAM Con

- Page 195 and 196:

Public Version www.ti.com SDRAM Con

- Page 197 and 198:

Public Version www.ti.com SDRAM Con

- Page 199 and 200:

Public Version www.ti.com SDRAM Con

- Page 201 and 202:

Public Version www.ti.com SDRAM Con

- Page 203 and 204:

Public Version www.ti.com SDRAM Con

- Page 205 and 206:

Public Version www.ti.com SDRAM Con

- Page 207 and 208:

Public Version www.ti.com SDRAM Con

- Page 209 and 210:

Public Version www.ti.com SDRAM Con

- Page 211 and 212:

Public Version www.ti.com SDRAM Con

- Page 213 and 214:

Public Version www.ti.com SDRAM Con

- Page 215 and 216:

Public Version www.ti.com SDRAM Con

- Page 217 and 218:

Public Version www.ti.com SDRAM Con

- Page 219 and 220:

Device D2D OCM_ROM OCM_RAM ROM (32K

- Page 221 and 222:

Public Version www.ti.com On-Chip M