Chapter 10 Memory Subsystem.pdf

Chapter 10 Memory Subsystem.pdf

Chapter 10 Memory Subsystem.pdf

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Public Version<br />

General-Purpose <strong>Memory</strong> Controller www.ti.com<br />

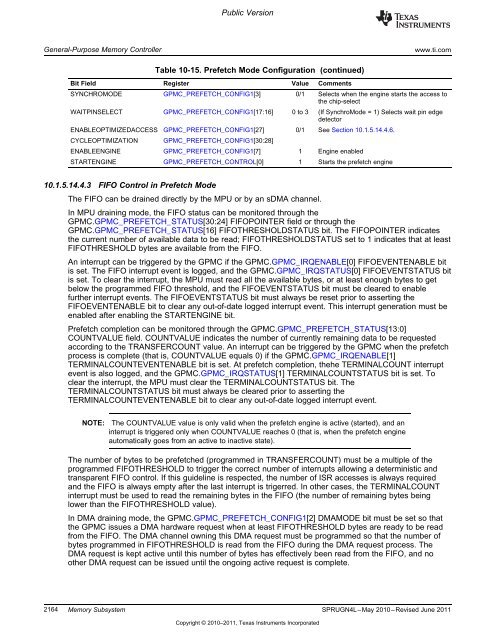

Table <strong>10</strong>-15. Prefetch Mode Configuration (continued)<br />

Bit Field Register Value Comments<br />

SYNCHROMODE GPMC_PREFETCH_CONFIG1[3] 0/1 Selects when the engine starts the access to<br />

the chip-select<br />

WAITPINSELECT GPMC_PREFETCH_CONFIG1[17:16] 0 to 3 (If SynchroMode = 1) Selects wait pin edge<br />

detector<br />

ENABLEOPTIMIZEDACCESS GPMC_PREFETCH_CONFIG1[27] 0/1 See Section <strong>10</strong>.1.5.14.4.6.<br />

CYCLEOPTIMIZATION GPMC_PREFETCH_CONFIG1[30:28]<br />

ENABLEENGINE GPMC_PREFETCH_CONFIG1[7] 1 Engine enabled<br />

STARTENGINE GPMC_PREFETCH_CONTROL[0] 1 Starts the prefetch engine<br />

<strong>10</strong>.1.5.14.4.3 FIFO Control in Prefetch Mode<br />

The FIFO can be drained directly by the MPU or by an sDMA channel.<br />

In MPU draining mode, the FIFO status can be monitored through the<br />

GPMC.GPMC_PREFETCH_STATUS[30:24] FIFOPOINTER field or through the<br />

GPMC.GPMC_PREFETCH_STATUS[16] FIFOTHRESHOLDSTATUS bit. The FIFOPOINTER indicates<br />

the current number of available data to be read; FIFOTHRESHOLDSTATUS set to 1 indicates that at least<br />

FIFOTHRESHOLD bytes are available from the FIFO.<br />

An interrupt can be triggered by the GPMC if the GPMC.GPMC_IRQENABLE[0] FIFOEVENTENABLE bit<br />

is set. The FIFO interrupt event is logged, and the GPMC.GPMC_IRQSTATUS[0] FIFOEVENTSTATUS bit<br />

is set. To clear the interrupt, the MPU must read all the available bytes, or at least enough bytes to get<br />

below the programmed FIFO threshold, and the FIFOEVENTSTATUS bit must be cleared to enable<br />

further interrupt events. The FIFOEVENTSTATUS bit must always be reset prior to asserting the<br />

FIFOEVENTENABLE bit to clear any out-of-date logged interrupt event. This interrupt generation must be<br />

enabled after enabling the STARTENGINE bit.<br />

Prefetch completion can be monitored through the GPMC.GPMC_PREFETCH_STATUS[13:0]<br />

COUNTVALUE field. COUNTVALUE indicates the number of currently remaining data to be requested<br />

according to the TRANSFERCOUNT value. An interrupt can be triggered by the GPMC when the prefetch<br />

process is complete (that is, COUNTVALUE equals 0) if the GPMC.GPMC_IRQENABLE[1]<br />

TERMINALCOUNTEVENTENABLE bit is set. At prefetch completion, thehe TERMINALCOUNT interrupt<br />

event is also logged, and the GPMC.GPMC_IRQSTATUS[1] TERMINALCOUNTSTATUS bit is set. To<br />

clear the interrupt, the MPU must clear the TERMINALCOUNTSTATUS bit. The<br />

TERMINALCOUNTSTATUS bit must always be cleared prior to asserting the<br />

TERMINALCOUNTEVENTENABLE bit to clear any out-of-date logged interrupt event.<br />

NOTE: The COUNTVALUE value is only valid when the prefetch engine is active (started), and an<br />

interrupt is triggered only when COUNTVALUE reaches 0 (that is, when the prefetch engine<br />

automatically goes from an active to inactive state).<br />

The number of bytes to be prefetched (programmed in TRANSFERCOUNT) must be a multiple of the<br />

programmed FIFOTHRESHOLD to trigger the correct number of interrupts allowing a deterministic and<br />

transparent FIFO control. If this guideline is respected, the number of ISR accesses is always required<br />

and the FIFO is always empty after the last interrupt is trigerred. In other cases, the TERMINALCOUNT<br />

interrupt must be used to read the remaining bytes in the FIFO (the number of remaining bytes being<br />

lower than the FIFOTHRESHOLD value).<br />

In DMA draining mode, the GPMC.GPMC_PREFETCH_CONFIG1[2] DMAMODE bit must be set so that<br />

the GPMC issues a DMA hardware request when at least FIFOTHRESHOLD bytes are ready to be read<br />

from the FIFO. The DMA channel owning this DMA request must be programmed so that the number of<br />

bytes programmed in FIFOTHRESHOLD is read from the FIFO during the DMA request process. The<br />

DMA request is kept active until this number of bytes has effectively been read from the FIFO, and no<br />

other DMA request can be issued until the ongoing active request is complete.<br />

2164 <strong>Memory</strong> <strong>Subsystem</strong> SPRUGN4L–May 20<strong>10</strong>–Revised June 2011<br />

Copyright © 20<strong>10</strong>–2011, Texas Instruments Incorporated