Chapter 10 Memory Subsystem.pdf

Chapter 10 Memory Subsystem.pdf

Chapter 10 Memory Subsystem.pdf

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

GPMC_FCLK<br />

GPMC_CLK<br />

gpmc_a[11:1]<br />

gpmc_d[15:0]<br />

nBE1nBE0<br />

nCS<br />

nADV<br />

nWE<br />

DIR<br />

WAIT<br />

Valid Address<br />

WRDATAONADMUXBUS<br />

Valid Address D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 D 7<br />

CSWROFFTIME<br />

CSONTIME<br />

ADVWROFFTIME<br />

ADVONTIME<br />

WEONTIME<br />

WRCYCLETIME0<br />

WRACCESSTIME PAGEBURSTACCESSTIME<br />

CLKACTIVATIONTIME<br />

WEOFFTIME<br />

Public Version<br />

www.ti.com General-Purpose <strong>Memory</strong> Controller<br />

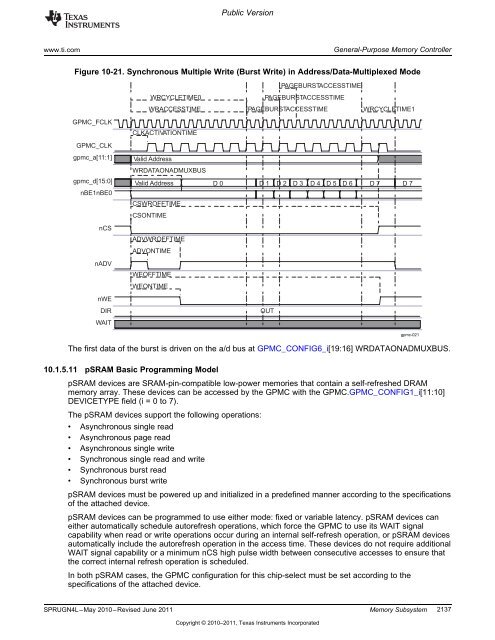

Figure <strong>10</strong>-21. Synchronous Multiple Write (Burst Write) in Address/Data-Multiplexed Mode<br />

PAGEBURSTACCESSTIME<br />

OUT<br />

PAGEBURSTACCESSTIME<br />

WRCYCLETIME1<br />

The first data of the burst is driven on the a/d bus at GPMC_CONFIG6_i[19:16] WRDATAONADMUXBUS.<br />

<strong>10</strong>.1.5.11 pSRAM Basic Programming Model<br />

pSRAM devices are SRAM-pin-compatible low-power memories that contain a self-refreshed DRAM<br />

memory array. These devices can be accessed by the GPMC with the GPMC.GPMC_CONFIG1_i[11:<strong>10</strong>]<br />

DEVICETYPE field (i = 0 to 7).<br />

The pSRAM devices support the following operations:<br />

• Asynchronous single read<br />

• Asynchronous page read<br />

• Asynchronous single write<br />

• Synchronous single read and write<br />

• Synchronous burst read<br />

• Synchronous burst write<br />

pSRAM devices must be powered up and initialized in a predefined manner according to the specifications<br />

of the attached device.<br />

pSRAM devices can be programmed to use either mode: fixed or variable latency. pSRAM devices can<br />

either automatically schedule autorefresh operations, which force the GPMC to use its WAIT signal<br />

capability when read or write operations occur during an internal self-refresh operation, or pSRAM devices<br />

automatically include the autorefresh operation in the access time. These devices do not require additional<br />

WAIT signal capability or a minimum nCS high pulse width between consecutive accesses to ensure that<br />

the correct internal refresh operation is scheduled.<br />

In both pSRAM cases, the GPMC configuration for this chip-select must be set according to the<br />

specifications of the attached device.<br />

SPRUGN4L–May 20<strong>10</strong>–Revised June 2011 <strong>Memory</strong> <strong>Subsystem</strong><br />

Copyright © 20<strong>10</strong>–2011, Texas Instruments Incorporated<br />

gpmc-021<br />

2137