Geode GXLV Processor Series Low Power Integrated x86 Solutions

Geode GXLV Processor Series Low Power Integrated x86 Solutions

Geode GXLV Processor Series Low Power Integrated x86 Solutions

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

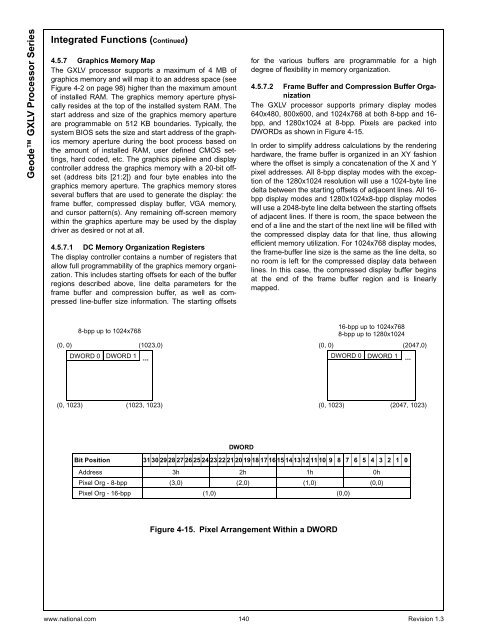

<strong>Geode</strong> <strong>GXLV</strong> <strong>Processor</strong> <strong>Series</strong><strong>Integrated</strong> Functions (Continued)4.5.7 Graphics Memory MapThe <strong>GXLV</strong> processor supports a maximum of 4 MB ofgraphics memory and will map it to an address space (seeFigure 4-2 on page 98) higher than the maximum amountof installed RAM. The graphics memory aperture physicallyresides at the top of the installed system RAM. Thestart address and size of the graphics memory apertureare programmable on 512 KB boundaries. Typically, thesystem BIOS sets the size and start address of the graphicsmemory aperture during the boot process based onthe amount of installed RAM, user defined CMOS settings,hard coded, etc. The graphics pipeline and displaycontroller address the graphics memory with a 20-bit offset(address bits [21:2]) and four byte enables into thegraphics memory aperture. The graphics memory storesseveral buffers that are used to generate the display: theframe buffer, compressed display buffer, VGA memory,and cursor pattern(s). Any remaining off-screen memorywithin the graphics aperture may be used by the displaydriver as desired or not at all.4.5.7.1 DC Memory Organization RegistersThe display controller contains a number of registers thatallow full programmability of the graphics memory organization.This includes starting offsets for each of the bufferregions described above, line delta parameters for theframe buffer and compression buffer, as well as compressedline-buffer size information. The starting offsetsfor the various buffers are programmable for a highdegree of flexibility in memory organization.4.5.7.2 Frame Buffer and Compression Buffer OrganizationThe <strong>GXLV</strong> processor supports primary display modes640x480, 800x600, and 1024x768 at both 8-bpp and 16-bpp, and 1280x1024 at 8-bpp. Pixels are packed intoDWORDs as shown in Figure 4-15.In order to simplify address calculations by the renderinghardware, the frame buffer is organized in an XY fashionwhere the offset is simply a concatenation of the X and Ypixel addresses. All 8-bpp display modes with the exceptionof the 1280x1024 resolution will use a 1024-byte linedelta between the starting offsets of adjacent lines. All 16-bpp display modes and 1280x1024x8-bpp display modeswill use a 2048-byte line delta between the starting offsetsof adjacent lines. If there is room, the space between theend of a line and the start of the next line will be filled withthe compressed display data for that line, thus allowingefficient memory utilization. For 1024x768 display modes,theframe-bufferlinesizeisthesameasthelinedelta,sono room is left for the compressed display data betweenlines. In this case, the compressed display buffer beginsat the end of the frame buffer region and is linearlymapped.(0, 0)8-bpp up to 1024x768DWORD 0DWORD 1(1023,0)(0, 0)16-bpp up to 1024x7688-bpp up to 1280x1024DWORD 0 DWORD 1... ...(2047,0)(0, 1023)(1023, 1023)(0, 1023)(2047, 1023)DWORDBit Position 31302928272625242322212019181716151413121110 9 8 7 6 5 4 3 2 1 0Address 3h 2h 1h 0hPixel Org - 8-bpp (3,0) (2,0) (1,0) (0,0)Pixel Org - 16-bpp (1,0) (0,0)Figure 4-15. Pixel Arrangement Within a DWORDwww.national.com 140 Revision 1.3