Geode GXLV Processor Series Low Power Integrated x86 Solutions

Geode GXLV Processor Series Low Power Integrated x86 Solutions

Geode GXLV Processor Series Low Power Integrated x86 Solutions

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

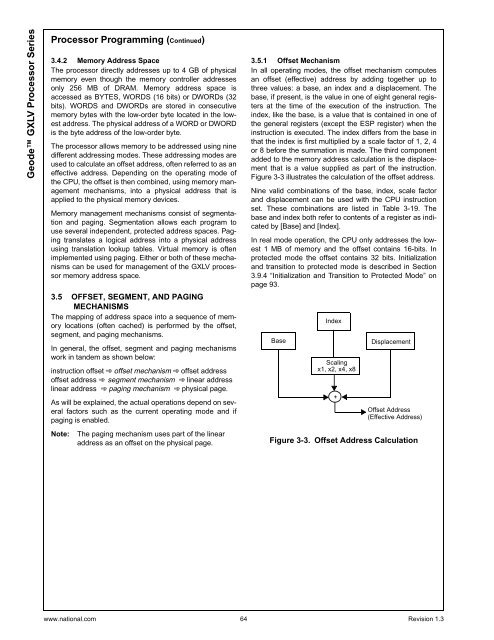

<strong>Geode</strong> <strong>GXLV</strong> <strong>Processor</strong> <strong>Series</strong><strong>Processor</strong> Programming (Continued)3.4.2 Memory Address SpaceThe processor directly addresses up to 4 GB of physicalmemory even though the memory controller addressesonly 256 MB of DRAM. Memory address space isaccessed as BYTES, WORDS (16 bits) or DWORDs (32bits). WORDS and DWORDs are stored in consecutivememory bytes with the low-order byte located in the lowestaddress. The physical address of a WORD or DWORDis the byte address of the low-order byte.The processor allows memory to be addressed using ninedifferent addressing modes. These addressing modes areused to calculate an offset address, often referred to as aneffective address. Depending on the operating mode ofthe CPU, the offset is then combined, using memory managementmechanisms, into a physical address that isapplied to the physical memory devices.Memory management mechanisms consist of segmentationand paging. Segmentation allows each program touse several independent, protected address spaces. Pagingtranslates a logical address into a physical addressusing translation lookup tables. Virtual memory is oftenimplemented using paging. Either or both of these mechanismscan be used for management of the <strong>GXLV</strong> processormemory address space.3.5 OFFSET, SEGMENT, AND PAGINGMECHANISMSThe mapping of address space into a sequence of memorylocations (often cached) is performed by the offset,segment, and paging mechanisms.In general, the offset, segment and paging mechanismswork in tandem as shown below:instruction offset offset mechanism offset addressoffset address segment mechanism linear addresslinear address paging mechanism physical page.As will be explained, the actual operations depend on severalfactors such as the current operating mode and ifpaging is enabled.Note:The paging mechanism uses part of the linearaddress as an offset on the physical page.3.5.1 Offset MechanismIn all operating modes, the offset mechanism computesan offset (effective) address by adding together up tothree values: a base, an index and a displacement. Thebase, if present, is the value in one of eight general registersat the time of the execution of the instruction. Theindex, like the base, is a value that is contained in one ofthe general registers (except the ESP register) when theinstruction is executed. The index differs from the base inthat the index is first multiplied by a scale factor of 1, 2, 4or 8 before the summation is made. The third componentadded to the memory address calculation is the displacementthat is a value supplied as part of the instruction.Figure 3-3 illustrates the calculation of the offset address.Nine valid combinations of the base, index, scale factorand displacement can be used with the CPU instructionset. These combinations are listed in Table 3-19. Thebase and index both refer to contents of a register as indicatedby [Base] and [Index].In real mode operation, the CPU only addresses the lowest1 MB of memory and the offset contains 16-bits. Inprotected mode the offset contains 32 bits. Initializationand transition to protected mode is described in Section3.9.4 “Initialization and Transition to Protected Mode” onpage 93.BaseIndexScalingx1, x2, x4, x8+DisplacementOffset Address(Effective Address)Figure 3-3. Offset Address Calculationwww.national.com 64 Revision 1.3