Geode GXLV Processor Series Low Power Integrated x86 Solutions

Geode GXLV Processor Series Low Power Integrated x86 Solutions

Geode GXLV Processor Series Low Power Integrated x86 Solutions

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

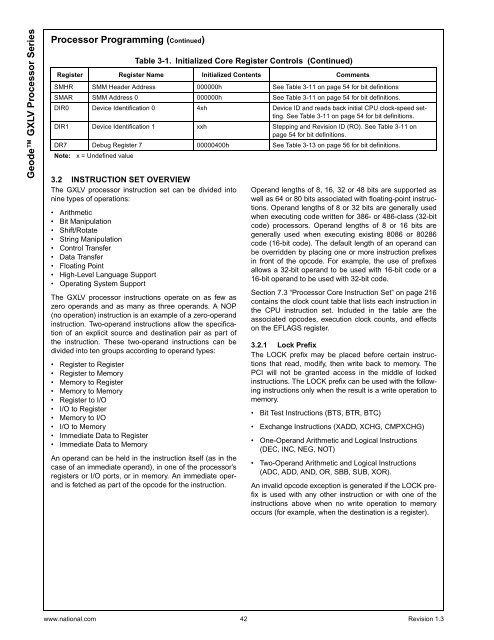

<strong>Geode</strong> <strong>GXLV</strong> <strong>Processor</strong> <strong>Series</strong><strong>Processor</strong> Programming (Continued)3.2 INSTRUCTION SET OVERVIEWThe <strong>GXLV</strong> processor instruction set can be divided intonine types of operations:• Arithmetic• Bit Manipulation• Shift/Rotate• String Manipulation• Control Transfer• Data Transfer• Floating Point• High-Level Language Support• Operating System SupportThe <strong>GXLV</strong> processor instructions operate on as few aszero operands and as many as three operands. A NOP(no operation) instruction is an example of a zero-operandinstruction. Two-operand instructions allow the specificationof an explicit source and destination pair as part ofthe instruction. These two-operand instructions can bedivided into ten groups according to operand types:• Register to Register• Register to Memory• Memory to Register• Memory to Memory• Register to I/O• I/O to Register• Memory to I/O• I/O to Memory• Immediate Data to Register• Immediate Data to MemoryTable 3-1. Initialized Core Register Controls (Continued)Register Register Name Initialized Contents CommentsSMHR SMM Header Address 000000h See Table 3-11 on page 54 for bit definitionsSMAR SMM Address 0 000000h See Table 3-11 on page 54 for bit definitions.DIR0 Device Identification 0 4xh Device ID and reads back initial CPU clock-speed setting.See Table 3-11 on page 54 for bit definitions.DIR1 Device Identification 1 xxh Stepping and Revision ID (RO). See Table 3-11 onpage 54 for bit definitions.DR7 Debug Register 7 00000400h See Table 3-13 on page 56 for bit definitions.Note: x = Undefined valueAnoperandcanbeheldintheinstructionitself(asinthecase of an immediate operand), in one of the processor’sregisters or I/O ports, or in memory. An immediate operandis fetched as part of the opcode for the instruction.Operand lengths of 8, 16, 32 or 48 bits are supported aswell as 64 or 80 bits associated with floating-point instructions.Operand lengths of 8 or 32 bits are generally usedwhen executing code written for 386- or 486-class (32-bitcode) processors. Operand lengths of 8 or 16 bits aregenerally used when executing existing 8086 or 80286code (16-bit code). The default length of an operand canbe overridden by placing one or more instruction prefixesin front of the opcode. For example, the use of prefixesallows a 32-bit operand to be used with 16-bit code or a16-bit operand to be used with 32-bit code.Section 7.3 “<strong>Processor</strong> Core Instruction Set” on page 216contains the clock count table that lists each instruction inthe CPU instruction set. Included in the table are theassociated opcodes, execution clock counts, and effectson the EFLAGS register.3.2.1 Lock PrefixThe LOCK prefix may be placed before certain instructionsthat read, modify, then write back to memory. ThePCI will not be granted access in the middle of lockedinstructions. The LOCK prefix can be used with the followinginstructions only when the result is a write operation tomemory.• Bit Test Instructions (BTS, BTR, BTC)• Exchange Instructions (XADD, XCHG, CMPXCHG)• One-Operand Arithmetic and Logical Instructions(DEC, INC, NEG, NOT)• Two-Operand Arithmetic and Logical Instructions(ADC, ADD, AND, OR, SBB, SUB, XOR).An invalid opcode exception is generated if the LOCK prefixis used with any other instruction or with one of theinstructions above when no write operation to memoryoccurs (for example, when the destination is a register).www.national.com 42 Revision 1.3