Geode GXLV Processor Series Low Power Integrated x86 Solutions

Geode GXLV Processor Series Low Power Integrated x86 Solutions

Geode GXLV Processor Series Low Power Integrated x86 Solutions

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

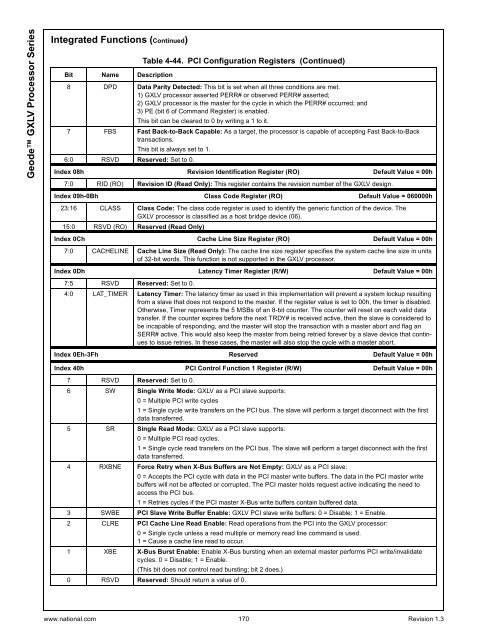

<strong>Geode</strong> <strong>GXLV</strong> <strong>Processor</strong> <strong>Series</strong><strong>Integrated</strong> Functions (Continued)Bit Name DescriptionTable 4-44. PCI Configuration Registers (Continued)8 DPD Data Parity Detected: This bit is set when all three conditions are met.1) <strong>GXLV</strong> processor asserted PERR# or observed PERR# asserted;2) <strong>GXLV</strong> processor is the master for the cycle in which the PERR# occurred; and3) PE (bit 6 of Command Register) is enabled.This bit can be cleared to 0 by writing a 1 to it.7 FBS Fast Back-to-Back Capable: As a target, the processor is capable of accepting Fast Back-to-Backtransactions.This bit is always set to 1.6:0 RSVD Reserved: Set to 0.Index 08h Revision Identification Register (RO) Default Value = 00h7:0 RID (RO) Revision ID (Read Only): This register contains the revision number of the <strong>GXLV</strong> design.Index 09h-0Bh Class Code Register (RO) Default Value = 060000h23:16 CLASS Class Code: The class code register is used to identify the generic function of the device. The<strong>GXLV</strong> processor is classified as a host bridge device (06).15:0 RSVD (RO) Reserved (Read Only)Index 0Ch Cache Line Size Register (RO) Default Value = 00h7:0 CACHELINE CacheLineSize(ReadOnly):The cache line size register specifies the system cache line size in unitsof 32-bit words. This function is not supported in the <strong>GXLV</strong> processor.Index 0Dh Latency Timer Register (R/W) Default Value = 00h7:5 RSVD Reserved: Set to 0.4:0 LAT_TIMER Latency Timer: The latency timer as used in this implementation will prevent a system lockup resultingfrom a slave that does not respond to the master. If the register value is set to 00h, the timer is disabled.Otherwise, Timer represents the 5 MSBs of an 8-bit counter. The counter will reset on each valid datatransfer. If the counter expires before the next TRDY# is received active, then the slave is considered tobe incapable of responding, and the master will stop the transaction with a master abort and flag anSERR# active. This would also keep the master from being retried forever by a slave device that continuesto issue retries. In these cases, the master will also stop the cycle with a master abort.Index 0Eh-3Fh Reserved Default Value = 00hIndex 40h PCI Control Function 1 Register (R/W) Default Value = 00h7 RSVD Reserved: Set to 0.6 SW Single Write Mode: <strong>GXLV</strong> as a PCI slave supports:0 = Multiple PCI write cycles1 = Single cycle write transfers on the PCI bus. The slave will perform a target disconnect with the firstdata transferred.5 SR Single Read Mode: <strong>GXLV</strong> as a PCI slave supports:0 = Multiple PCI read cycles.1 = Single cycle read transfers on the PCI bus. The slave will perform a target disconnect with the firstdata transferred.4 RXBNE Force Retry when X-Bus Buffers are Not Empty: <strong>GXLV</strong> as a PCI slave:0 = Accepts the PCI cycle with data in the PCI master write buffers. The data in the PCI master writebuffers will not be affected or corrupted. The PCI master holds request active indicating the need toaccess the PCI bus.1 = Retries cycles if the PCI master X-Bus write buffers contain buffered data.3 SWBE PCI Slave Write Buffer Enable: <strong>GXLV</strong> PCI slave write buffers: 0 = Disable; 1 = Enable.2 CLRE PCI Cache Line Read Enable: Read operations from the PCI into the <strong>GXLV</strong> processor:0 = Single cycle unless a read multiple or memory read line command is used.1 = Cause a cache line read to occur.1 XBE X-Bus Burst Enable: Enable X-Bus bursting when an external master performs PCI write/invalidatecycles. 0 = Disable; 1 = Enable.(This bit does not control read bursting; bit 2 does.)0 RSVD Reserved: Should return a value of 0.www.national.com 170 Revision 1.3