Cortex-A8 Technical Reference Manual - ARM Information Center

Cortex-A8 Technical Reference Manual - ARM Information Center

Cortex-A8 Technical Reference Manual - ARM Information Center

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

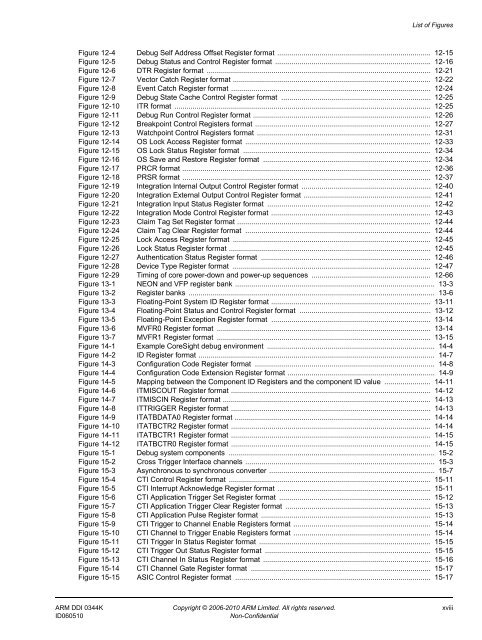

List of Figures<br />

Figure 12-4 Debug Self Address Offset Register format ............................................................................ 12-15<br />

Figure 12-5 Debug Status and Control Register format ............................................................................. 12-16<br />

Figure 12-6 DTR Register format ............................................................................................................... 12-21<br />

Figure 12-7 Vector Catch Register format .................................................................................................. 12-22<br />

Figure 12-8 Event Catch Register format ................................................................................................... 12-24<br />

Figure 12-9 Debug State Cache Control Register format .......................................................................... 12-25<br />

Figure 12-10 ITR format ............................................................................................................................... 12-25<br />

Figure 12-11 Debug Run Control Register format ........................................................................................ 12-26<br />

Figure 12-12 Breakpoint Control Registers format ....................................................................................... 12-27<br />

Figure 12-13 Watchpoint Control Registers format ...................................................................................... 12-31<br />

Figure 12-14 OS Lock Access Register format ............................................................................................ 12-33<br />

Figure 12-15 OS Lock Status Register format ............................................................................................. 12-34<br />

Figure 12-16 OS Save and Restore Register format ................................................................................... 12-34<br />

Figure 12-17 PRCR format ........................................................................................................................... 12-36<br />

Figure 12-18 PRSR format ........................................................................................................................... 12-37<br />

Figure 12-19 Integration Internal Output Control Register format ................................................................ 12-40<br />

Figure 12-20 Integration External Output Control Register format ............................................................... 12-41<br />

Figure 12-21 Integration Input Status Register format ................................................................................. 12-42<br />

Figure 12-22 Integration Mode Control Register format ............................................................................... 12-43<br />

Figure 12-23 Claim Tag Set Register format ................................................................................................ 12-44<br />

Figure 12-24 Claim Tag Clear Register format ............................................................................................ 12-44<br />

Figure 12-25 Lock Access Register format .................................................................................................. 12-45<br />

Figure 12-26 Lock Status Register format .................................................................................................... 12-45<br />

Figure 12-27 Authentication Status Register format .................................................................................... 12-46<br />

Figure 12-28 Device Type Register format .................................................................................................. 12-47<br />

Figure 12-29 Timing of core power-down and power-up sequences ........................................................... 12-66<br />

Figure 13-1 NEON and VFP register bank ................................................................................................... 13-3<br />

Figure 13-2 Register banks .......................................................................................................................... 13-6<br />

Figure 13-3 Floating-Point System ID Register format ............................................................................... 13-11<br />

Figure 13-4 Floating-Point Status and Control Register format ................................................................. 13-12<br />

Figure 13-5 Floating-Point Exception Register format ............................................................................... 13-14<br />

Figure 13-6 MVFR0 Register format .......................................................................................................... 13-14<br />

Figure 13-7 MVFR1 Register format .......................................................................................................... 13-15<br />

Figure 14-1 Example CoreSight debug environment ................................................................................... 14-4<br />

Figure 14-2 ID Register format ..................................................................................................................... 14-7<br />

Figure 14-3 Configuration Code Register format ......................................................................................... 14-8<br />

Figure 14-4 Configuration Code Extension Register format ......................................................................... 14-9<br />

Figure 14-5 Mapping between the Component ID Registers and the component ID value ....................... 14-11<br />

Figure 14-6 ITMISCOUT Register format ................................................................................................... 14-12<br />

Figure 14-7 ITMISCIN Register format ....................................................................................................... 14-13<br />

Figure 14-8 ITTRIGGER Register format ................................................................................................... 14-13<br />

Figure 14-9 ITATBDATA0 Register format ................................................................................................. 14-14<br />

Figure 14-10 ITATBCTR2 Register format ................................................................................................... 14-14<br />

Figure 14-11 ITATBCTR1 Register format ................................................................................................... 14-15<br />

Figure 14-12 ITATBCTR0 Register format ................................................................................................... 14-15<br />

Figure 15-1 Debug system components ...................................................................................................... 15-2<br />

Figure 15-2 Cross Trigger Interface channels .............................................................................................. 15-3<br />

Figure 15-3 Asynchronous to synchronous converter .................................................................................. 15-7<br />

Figure 15-4 CTI Control Register format .................................................................................................... 15-11<br />

Figure 15-5 CTI Interrupt Acknowledge Register format ............................................................................ 15-11<br />

Figure 15-6 CTI Application Trigger Set Register format ........................................................................... 15-12<br />

Figure 15-7 CTI Application Trigger Clear Register format ........................................................................ 15-13<br />

Figure 15-8 CTI Application Pulse Register format .................................................................................... 15-13<br />

Figure 15-9 CTI Trigger to Channel Enable Registers format .................................................................... 15-14<br />

Figure 15-10 CTI Channel to Trigger Enable Registers format .................................................................... 15-14<br />

Figure 15-11 CTI Trigger In Status Register format ..................................................................................... 15-15<br />

Figure 15-12 CTI Trigger Out Status Register format .................................................................................. 15-15<br />

Figure 15-13 CTI Channel In Status Register format ................................................................................... 15-16<br />

Figure 15-14 CTI Channel Gate Register format ......................................................................................... 15-17<br />

Figure 15-15 ASIC Control Register format ................................................................................................. 15-17<br />

<strong>ARM</strong> DDI 0344K Copyright © 2006-2010 <strong>ARM</strong> Limited. All rights reserved. xviii<br />

ID060510 Non-Confidential