ARM Cortex-A15 MPCore Processor Technical Reference Manual

ARM Cortex-A15 MPCore Processor Technical Reference Manual

ARM Cortex-A15 MPCore Processor Technical Reference Manual

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

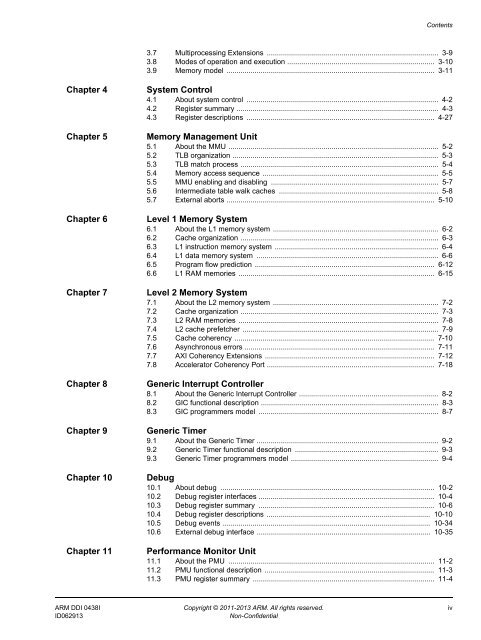

Contents3.7 Multiprocessing Extensions ..................................................................................... 3-93.8 Modes of operation and execution ......................................................................... 3-103.9 Memory model ....................................................................................................... 3-11Chapter 4Chapter 5Chapter 6Chapter 7Chapter 8Chapter 9Chapter 10Chapter 11System Control4.1 About system control ............................................................................................... 4-24.2 Register summary .................................................................................................... 4-34.3 Register descriptions ............................................................................................. 4-27Memory Management Unit5.1 About the MMU ........................................................................................................ 5-25.2 TLB organization ...................................................................................................... 5-35.3 TLB match process .................................................................................................. 5-45.4 Memory access sequence ....................................................................................... 5-55.5 MMU enabling and disabling ................................................................................... 5-75.6 Intermediate table walk caches ............................................................................... 5-85.7 External aborts ....................................................................................................... 5-10Level 1 Memory System6.1 About the L1 memory system .................................................................................. 6-26.2 Cache organization .................................................................................................. 6-36.3 L1 instruction memory system ................................................................................. 6-46.4 L1 data memory system .......................................................................................... 6-66.5 Program flow prediction ......................................................................................... 6-126.6 L1 RAM memories ................................................................................................. 6-15Level 2 Memory System7.1 About the L2 memory system .................................................................................. 7-27.2 Cache organization .................................................................................................. 7-37.3 L2 RAM memories ................................................................................................... 7-87.4 L2 cache prefetcher ................................................................................................. 7-97.5 Cache coherency ................................................................................................... 7-107.6 Asynchronous errors .............................................................................................. 7-117.7 AXI Coherency Extensions .................................................................................... 7-127.8 Accelerator Coherency Port ................................................................................... 7-18Generic Interrupt Controller8.1 About the Generic Interrupt Controller ..................................................................... 8-28.2 GIC functional description ........................................................................................ 8-38.3 GIC programmers model ......................................................................................... 8-7Generic Timer9.1 About the Generic Timer .......................................................................................... 9-29.2 Generic Timer functional description ....................................................................... 9-39.3 Generic Timer programmers model ......................................................................... 9-4Debug10.1 About debug .......................................................................................................... 10-210.2 Debug register interfaces ....................................................................................... 10-410.3 Debug register summary ....................................................................................... 10-610.4 Debug register descriptions ................................................................................. 10-1010.5 Debug events ....................................................................................................... 10-3410.6 External debug interface ...................................................................................... 10-35Performance Monitor Unit11.1 About the PMU ...................................................................................................... 11-211.2 PMU functional description .................................................................................... 11-311.3 PMU register summary .......................................................................................... 11-4<strong>ARM</strong> DDI 0438I Copyright © 2011-2013 <strong>ARM</strong>. All rights reserved. ivID062913Non-Confidential